# Physik-Department

## **Dissertation**

Search for  $D^+ \to K^- K^0_S \pi^+ \pi^+ \pi^0$  at the Belle Experiment and

Development of the Read-Out System for the Pixel Detector of the Belle II Experiment

Dmytro Levit

Technische Universität München

# Technische Universität München Physik-Department

Search for

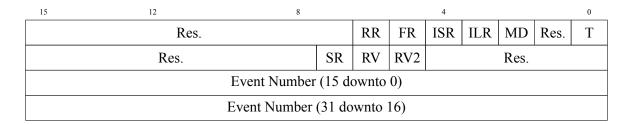

$$D^+ \to K^- K^0_S \pi^+ \pi^+ \pi^0$$

at the Belle

Experiment

and

# Development of the Read-Out System for the Pixel Detector of the Belle II Experiment

Dmytro Levit

Vollständiger Abdruck der von der Fakultät für Physik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr. Andreas Weiler

Prüfer der Dissertation: 1. Prof. Dr. Stephan Paul

2. Prof. Dr. Christian Kiesling

Die Dissertation wurde am 12.12.2018 bei der Technischen Universität München eingereicht und durch die Fakultät für Physik am 23.01.2019 angenommen.

#### Abstract

The thesis describes development of a read-out system of the pixel detector at Belle II and search for a rare D<sup>+</sup> decay in full data sample of Belle experiment. Channel D<sup>+</sup>  $\rightarrow$  K<sup>-</sup>K<sup>0</sup><sub>S</sub> $\pi^+\pi^+\pi^0$  is sensitive to new physics models that manifest themself in CP-violating isospin transition amplitudes  $\Delta I = \frac{3}{2}$ , which are prohibited in the standard model. This channel allows us to measure CP violation in the  $\Delta I = \frac{3}{2}$  amplitude. I measured branching fraction with weak statistical significance 2  $\sigma$ , and therefore report a 95 % upper exclusive limit on the branching fraction

$$BF(D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0) < 7.23 \cdot 10^{-5}.$$

In the second part of the thesis, I describe an FPGA-based read-out system for the DEPFET pixel detector of the new Belle II experiment. The system controls the pixel detector and processes its data as a stand-alone data acquisition system for detector development and characterization and as a high-performance read-out system at Belle II.

#### Zusammenfassung

Die Dissertation befasst sich mit dem Aufbau des Datenerfassungssystems für den Pixeldetektor in Belle II und der Suche nach einem seltenen Zerfall des D<sup>+</sup> Mesons in dem gesamten Datensatz des Belle Experiments. Der Zerfall D<sup>+</sup>  $\rightarrow$  K<sup>-</sup>K $_{S}^{0}\pi^{+}\pi^{+}\pi^{0}$  könnte Physik jenseits des Standardmodels ausschließen. Durch diesen Zerfall könnten wir die, im Standardmodell verbotenen, CP-verletzenden  $\Delta I = \frac{3}{2}$  Amplituden messen. Ich habe das Verzweigungsverhältnis mit schwacher statistischer Signifikanz 2  $\sigma$  gemessen und die 95 % obere Ausschlussgrenze für das Verzweigungsverhältnis

$$BF(D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0) < 7.23 \cdot 10^{-5}$$

bestimmt. Im zweiten Teil meiner Arbeit beschreibe ich ein FPGA-basiertes Auslesesystem für den Belle II Pixeldetektor. Das System steuert den Detektor und verarbeitet seine Daten als Datenerfassungssystem für Detektorenentwicklung und -charakterisierung und als schnelles Auslesesystem in Belle II.

# Contents

| 1. | Intro | oduction                                                   | 11 |

|----|-------|------------------------------------------------------------|----|

| 2. | The   | Standard Model and the CP Violation                        | 15 |

|    | 2.1.  | Discrete Space-Time Symmetries in the Standard Model       | 15 |

|    |       | 2.1.1. Parity Symmetry Violation                           | 16 |

|    |       | 2.1.2. Charge Conjugation Symmetry Violation               | 16 |

|    | 2.2.  | CP Violation                                               | 16 |

|    | 2.3.  | CP Violating Amplitudes                                    | 17 |

|    | 2.4.  | Cabibbo-Kobayashi-Maskawa Matrix                           | 18 |

| 3. | CP .  | Violation in Charm Sector as a Probe for the New Physics   | 21 |

|    | 3.1.  | Measurement of CP Violation in Charm                       | 21 |

|    |       | 3.1.1. Tree-Level Operators                                | 22 |

|    |       | 3.1.2. Penguin Operators                                   | 23 |

|    |       | 3.1.3. CP Violation in $\Delta I = \frac{3}{2}$ Amplitudes | 24 |

|    | 3.2.  | Decay $D^+ \to K^*K^*\pi$                                  | 26 |

| 4. | Belle | e Experiment                                               | 29 |

|    | 4.1.  | KEKB B Factory                                             | 29 |

|    | 4.2.  | Belle Detector                                             | 30 |

|    |       | 4.2.1. Silicon Vertex detector                             | 30 |

|    |       | 4.2.2. Central Drift Chamber                               | 32 |

|    |       | 4.2.3. Particle Identification Detectors                   | 32 |

|    |       | 4.2.4. Electromagnetic Calorimeter                         | 33 |

| 5. | Sear  | ch for the Decay $D^+ 	o K^- K^0_S \pi^+ \pi^+ \pi^0$      | 35 |

|    | 5.1.  | Analysis Overview                                          | 35 |

|    | 5.2.  | Monte Carlo Simulations                                    | 36 |

|    | 5.3.  | Event Selection                                            | 36 |

|    |       | 5.3.1. Geometric Acceptance and Selection Efficiency       | 37 |

|    | 5.4.  | Post-Skim Event Selection                                  | 39 |

|    |       | 5.4.1. Background Reduction with Boosted Decision Trees    | 39 |

|    |       | 5.4.2. Best Candidate Selection                            | 40 |

|    |       | 5.4.3. Final Cuts                                          | 41 |

|    |       | 5.4.4. Background Studies                                  | 44 |

|    |       | 5.4.5. Peaking Component in the Background Distribution    |    |

|    |       | 5.1.6. Efficiency Corrections                              | 17 |

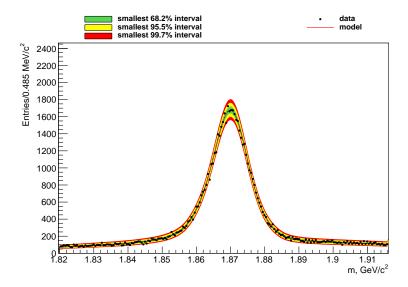

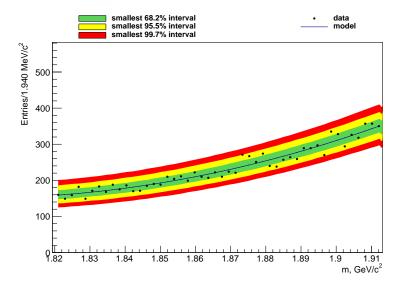

|    | 5.5.  | Fit to the Data                                                                                                | 51  |

|----|-------|----------------------------------------------------------------------------------------------------------------|-----|

|    |       | 5.5.1. Signal Shape                                                                                            | 51  |

|    |       | 5.5.2. Background Shape                                                                                        | 52  |

|    |       | 5.5.3. Combined Fits                                                                                           | 52  |

|    |       | 5.5.4. Sensitivity Scans                                                                                       | 54  |

|    | 5.6.  | Cross Checks                                                                                                   | 56  |

|    | 5.7.  | Cross Checks with 10 % Data Sample                                                                             | 61  |

|    | 5.8.  | Systematic Uncertainties                                                                                       | 63  |

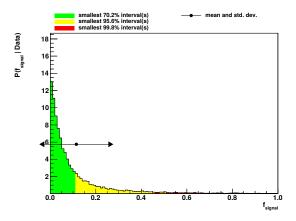

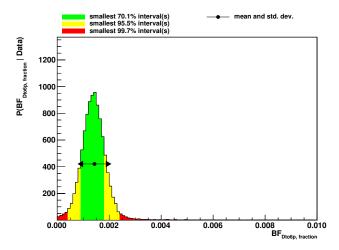

|    | 5.9.  |                                                                                                                | 66  |

|    | 5.10. | Improvement of the Measurements                                                                                | 69  |

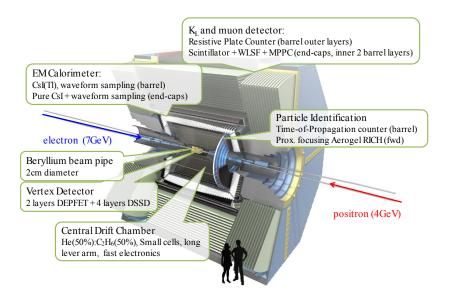

| 6. | Belle | e II Experiment                                                                                                | 73  |

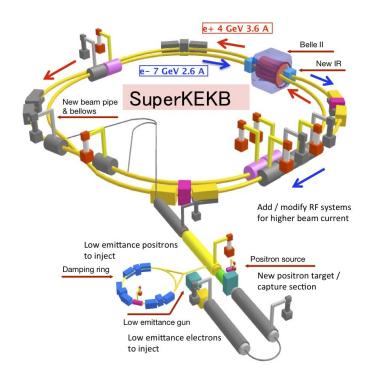

| -  | 6.1.  | SuperKEKB Collider                                                                                             | 73  |

|    | 6.2.  | Central Drift Chamber                                                                                          | 75  |

|    | 6.3.  | Aerogel Ring Imaging Cherenkov Detector                                                                        | 76  |

|    | 6.4.  | Time-of-Propagation Counter                                                                                    | 78  |

|    | 6.5.  | Electromagnetic Calorimeter                                                                                    | 78  |

|    |       | $K_L^0$ and Muon Detector                                                                                      | 79  |

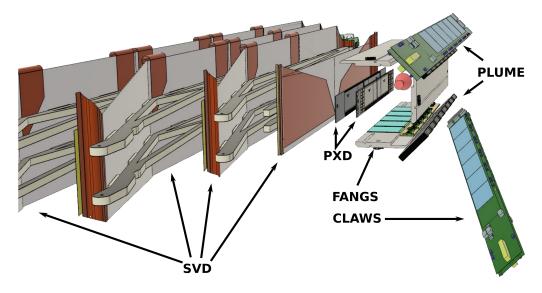

| 7. | Vort  | ex Detector                                                                                                    | 81  |

| 1. | 7.1.  | Silicon Strip Detector                                                                                         | 83  |

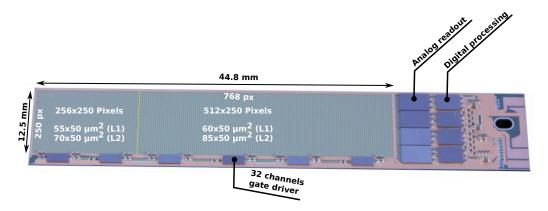

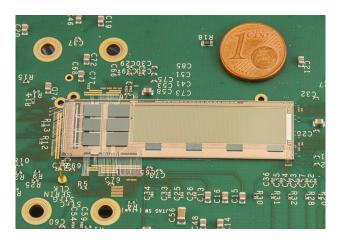

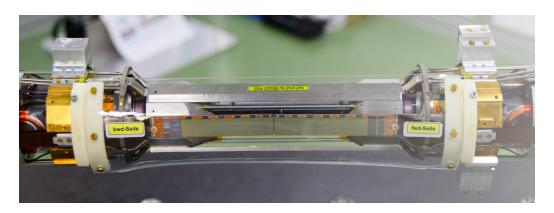

|    | 7.1.  | Pixel Detector                                                                                                 | 84  |

|    | 1.4.  |                                                                                                                | 84  |

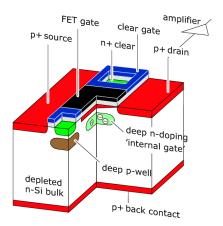

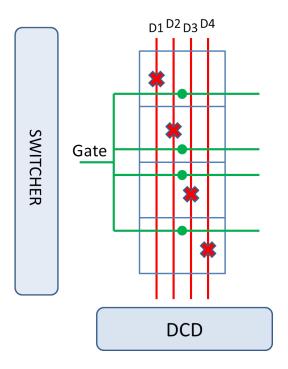

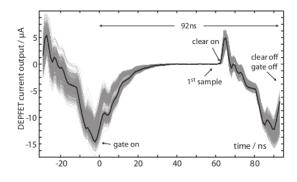

|    |       | 7.2.1. DEPFET Technology                                                                                       | 85  |

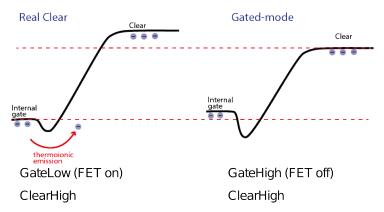

|    |       | 7.2.3. Intrinsic Electronic Shutter                                                                            | 86  |

|    |       |                                                                                                                | 86  |

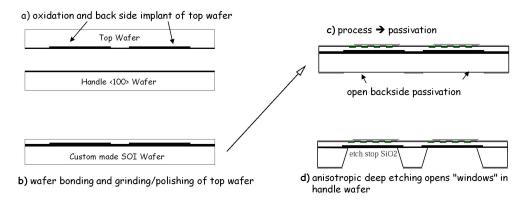

|    |       | E                                                                                                              | 90  |

|    |       | , and the second se | 90  |

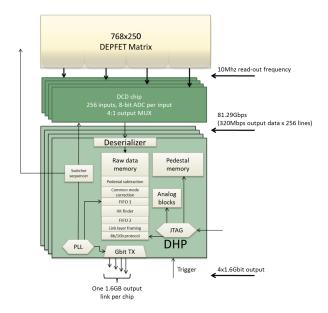

|    |       | 7.2.6. Front-end Electronics                                                                                   | 90  |

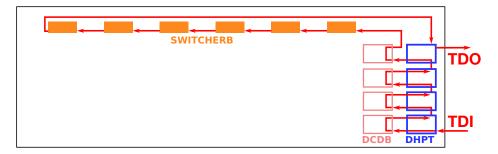

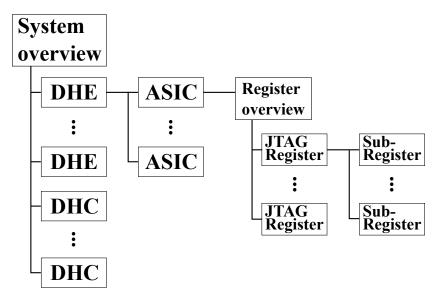

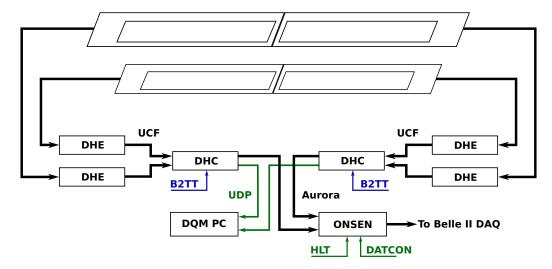

| 8. |       | Read-Out System of the Pixel Detector                                                                          | 95  |

|    | 8.1.  | 1                                                                                                              | 97  |

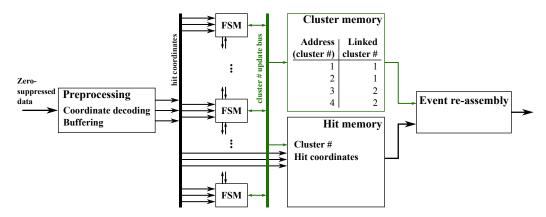

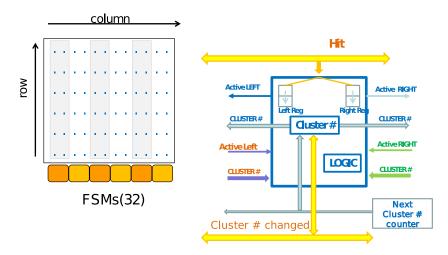

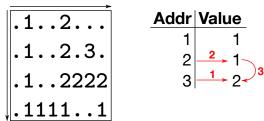

|    |       | 8.1.1. Data Processing                                                                                         | 97  |

|    | 8.2.  | $\mathcal{E}$                                                                                                  |     |

|    | 8.3.  | Hardware Components                                                                                            |     |

|    |       |                                                                                                                | 101 |

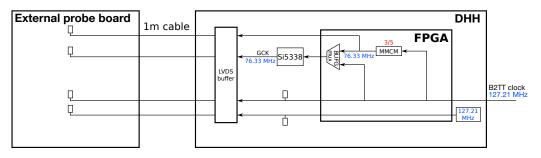

|    |       | 8.3.2. Programmable Clock Synthesizer Si5338                                                                   |     |

|    |       | 8.3.3. DHH AMC Modules                                                                                         |     |

|    |       | 8.3.4. VME Carrier Board                                                                                       | 105 |

|    |       |                                                                                                                | 107 |

|    |       | 8.3.6. Optical Transmitters                                                                                    |     |

|    |       | 8.3.7. Data Handling Insulator                                                                                 | 110 |

|    | 8.4.  | ~,~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                        | 111 |

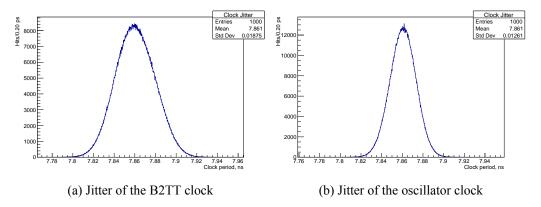

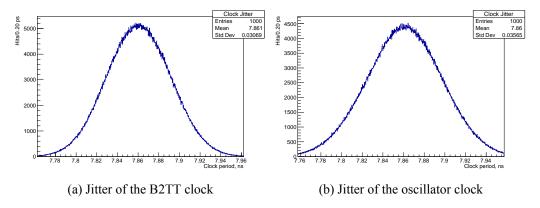

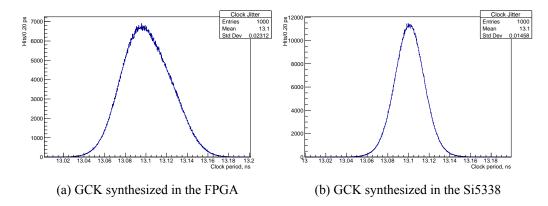

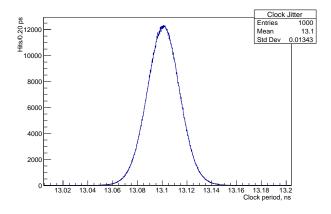

|    |       | 8.4.1. Quality of the Clock                                                                                    |     |

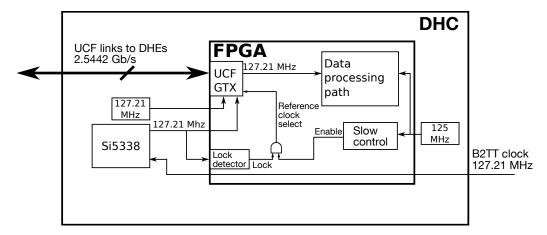

|    |       | 8.4.2. Clock Processing in the DHC                                                                             | 115 |

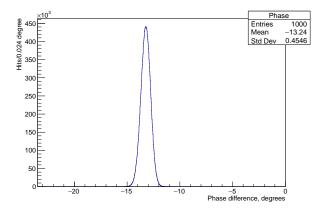

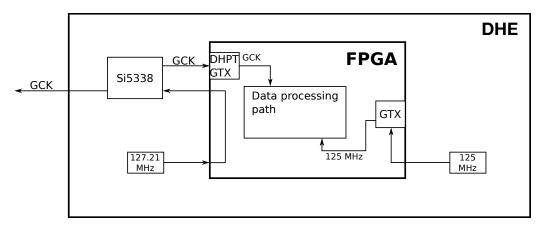

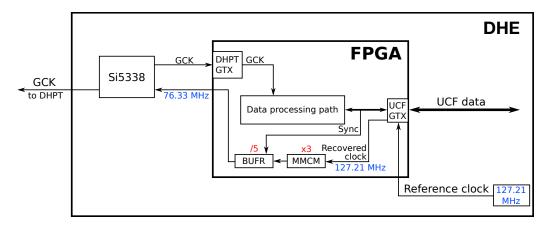

|    |       | 8.4.3. Clock Processing in the DHE                            | 116        |

|----|-------|---------------------------------------------------------------|------------|

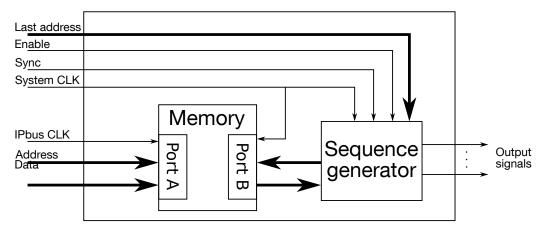

|    | 8.5.  | Data Handling Engine                                          | 117        |

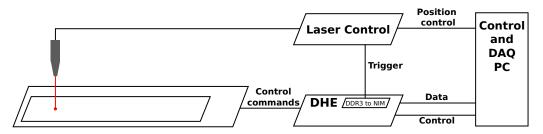

|    |       | 8.5.1. Standalone System for Laboratory Setups and Beam Tests | 117        |

|    |       | 8.5.2. DHE System for Belle II                                | 125        |

|    | 8.6.  | Data Handling Concentrator                                    | 132        |

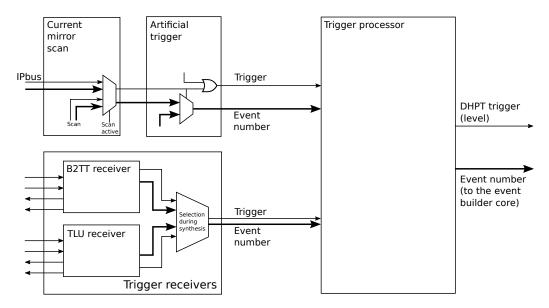

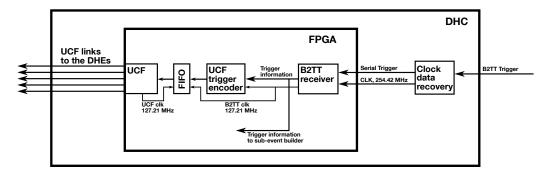

|    |       | 8.6.1. Trigger Processing                                     | 133        |

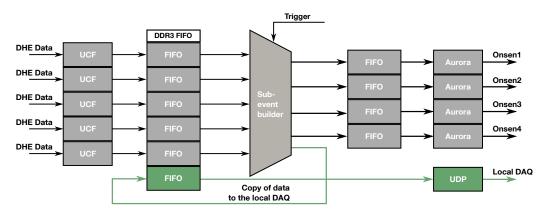

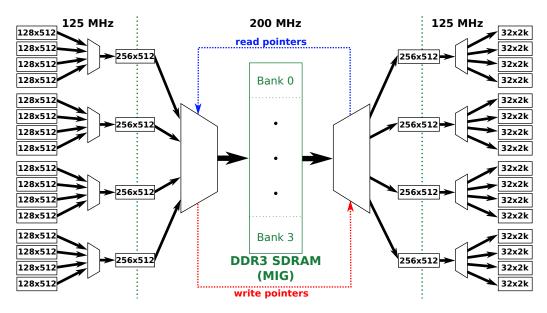

|    |       | 8.6.2. Data Processing                                        | 134        |

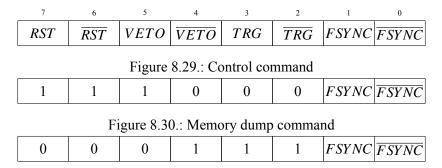

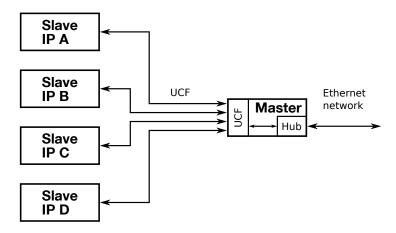

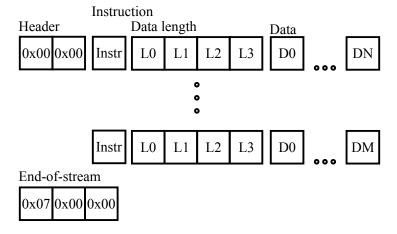

|    | 8.7.  | Unified Communication Protocol                                | 136        |

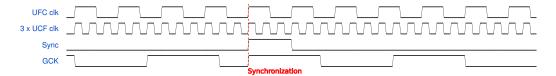

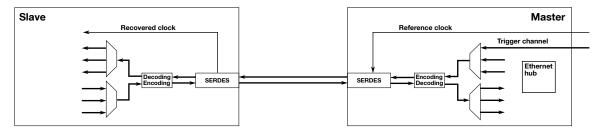

|    |       | 8.7.1. Clock Phase Synchronization                            | 137        |

|    |       | 8.7.2. Link Operation                                         | 141        |

|    |       | 8.7.3. Ethernet Hub                                           | 142        |

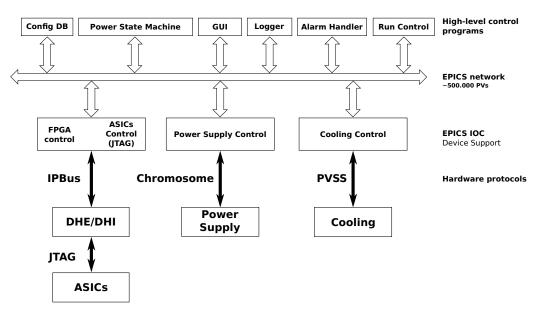

|    | 8.8.  | Slow Control                                                  | 143        |

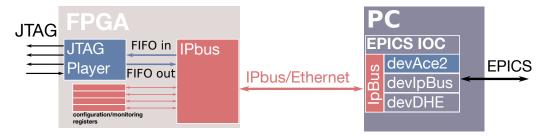

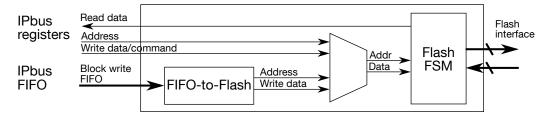

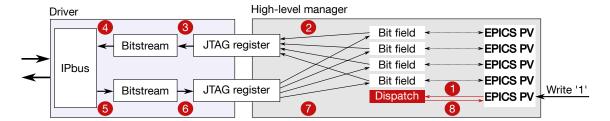

|    |       | 8.8.1. IPbus                                                  | 144        |

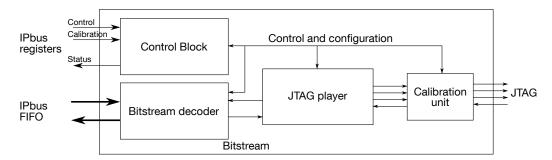

|    |       | 8.8.2. IPbus Cores                                            | 145        |

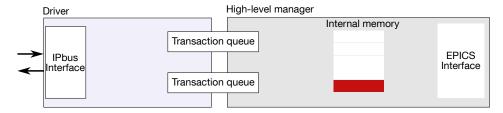

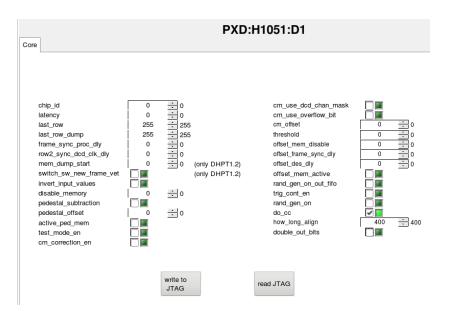

|    |       | 8.8.3. Control Software                                       | 149        |

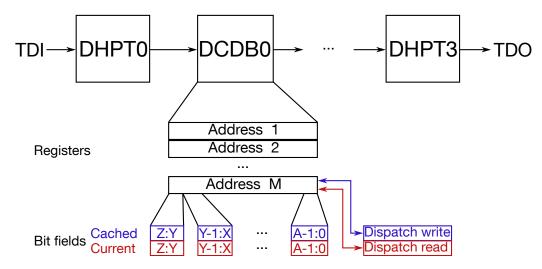

|    |       | 8.8.4. JTAG Control Software                                  | 151        |

|    |       |                                                               |            |

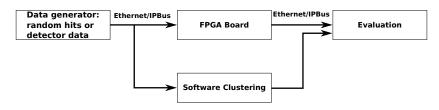

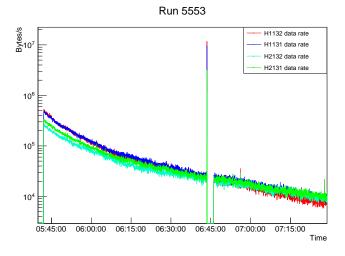

| 9. |       | s of the Read-Out System                                      | 157        |

|    | 9.1.  | Combined Beam Test at DESY                                    |            |

|    |       | 9.1.1. Pixel Detector and the DHH System at the Beam Test     |            |

|    |       | 9.1.2. Read-out Chain                                         |            |

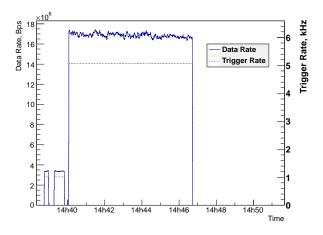

|    |       | 9.1.3. Results of the Beam Test                               |            |

|    |       |                                                               |            |

|    | 9.3.  | 1                                                             |            |

|    |       | 9.3.1. Pixel Detector in the Phase 2                          |            |

|    |       | 9.3.2. DHH System in the Phase 2                              | 164        |

| 10 | . Sum | nmary and Conclusions                                         | 167        |

| A  | 1     | 1:                                                            | 100        |

| A  | pend  |                                                               | 169        |

|    | A.    | BDT Parameters                                                |            |

|    | В.    |                                                               |            |

|    |       | B.1. Process Variables in the DHE                             |            |

|    | 0     | B.2. Process Variables in the DHC                             |            |

|    | C.    | JTAG Bitstream Format                                         |            |

|    | D.    | Parameters of the EPICS IOC                                   |            |

|    | E.    | Format of the UDP Frames                                      |            |

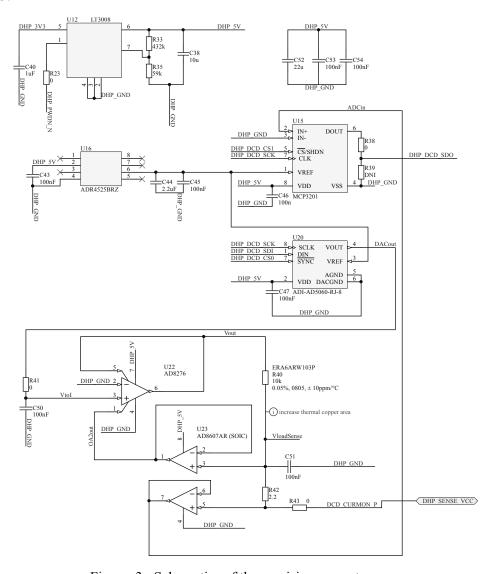

|    | F.    | Schematics of the Current Mirror                              |            |

|    | G.    | Format of the UCF Trigger Frame                               | 184<br>185 |

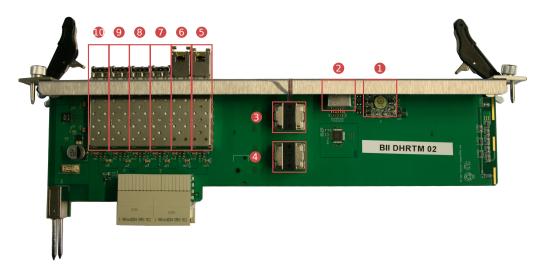

|    | Н     | ALL A Larrier Board and Rear Transition Module                | 1 × 5      |

# Chapter 1.

## Introduction

The visible universe is made out of matter and not a matter-antimatter mixture. We know this fact from studying matter-antimatter composition of the cosmic rays. Also, we do not observe matter-antimatter annihilation signature in high-energy cosmic gamma rays.

There are two production mechanisms of the cosmic rays: the primary and the secondary production. The primary-produced rays originate in the stellar objects that radiate its constituents into the universe. For example, supernovae explosions or gas acceleration in the active galactic nuclei produce the rays of charged particles. These rays carry the information about the composition of the object.

If primary rays collide with cosmic background radiation in space they produce matter and antimatter rays. This type of rays is called the secondary rays. We can identify primary and secondary rays by their energy spectrum which differs for each type of the cosmic rays. Therefore, by measuring energy of the cosmic rays we can remove contribution of the secondary rays and calculate the matter-antimatter content of the universe [1].

The AMS-02 collaboration used this approach to measure the matter-antimatter composition of the visible universe. The experiment measured the amounts of matter and antimatter in the cosmic rays reaching Earth [2]. The measured fraction of the antimatter in the cosmic rays is consistent with secondary antimatter production in space from the collisions of the cosmic rays. This measurement proves that the visible universe consists only of matter.

This raises the question about the origin of matter-antimatter asymmetry in the universe. Scientists believe that most matter and all antimatter produced early in the universe annihilated with each other approximately 400000 years after the big bang. The photons from matter-antimatter annihilation form the cosmic background radiation. An excess of matter survived and formed our visible universe.

Because the universe is matter dominated, we can describe matter-antimatter asymmetry

$$A_{univ} = \frac{M - \overline{M}}{M + \overline{M}} \tag{1.1}$$

as a ratio of matter that is still around today  $M - \overline{M}$  to the sum of matter and antimatter produced by the big bang  $M + \overline{M}$ .

Under assumption of baryon number conservation we know that all baryons, which survived annihilation in the early universe, have to be present today in form of baryonic matter. We estimate quantity of matter which survived annihilation from baryon density,

$n_B$ , measured by AMS-02. We estimate the sum of matter and antimatter from the density of photons,  $n_{\gamma}$ , in the cosmic microwave background measured by the Planck collaboration [3]. With these quantities we estimate the matter-antimatter asymmetry in the early universe

$$A_{univ} = \frac{n_B}{n_\gamma} \approx 6 \times 10^{-10} [1]. \tag{1.2}$$

This asymmetry originates in the baryogenesis process that produced matter. In 1966 Sakharov proposed three conditions that are necessary during baryogenesis to produce the matter-dominated universe [4]. The Sakharov conditions are that baryogenesis processes:

- 1. proceed in thermal inequilibrium,

- 2. violate baryon number, and

- 3. violate discrete charge-parity (CP) symmetry.

The first condition is fulfilled because baryogenesis takes place in the expanding universe. Violation of baryon number has not yet been observed experimentally; but the standard model of particle physics allows for the baryon number violation at energies not currently reachable experimentally. Violation of the CP symmetry has been observed experimentally in the decays of kaons and beauty hadrons. The standard model incorporates CP violation through the structure of the weak interaction. However, the matter-antimatter asymmetry of the universe is 10 orders of magnitude larger than what the standard model could explain.

This discrepancy between observation and theory tells us that our understanding of the universe is not complete. So we search for new sources of CP violation beyond the standard model. A possible source of CP violation beyond the standard model may be found in the decays of the charm quark. Standard model prediction of the CP violation of the charm quark is two orders of magnitude below the current experimental sensitivity. This leaves room for discovering CP violation effects beyond the standard model predictions in decays of charmed hadrons.

This thesis starts with description of a search for non-standard-model sources of the CP violation in decay of  $D^+$ . I measured the branching fraction of the decay  $D^+ \to K^-K^0_S\pi^+\pi^+\pi^0$  using full data set of  $1\,ab^{-1}$  recorded at the Belle experiment. This decay is sensitive to a subset of the CP-violating models beyond the standard model that have the weak  $\Delta I = \frac{3}{2}$  structure.

While having the largest data sample, many measurements done at Belle still do not reach the desired sensitivity because the standard model predicts low rate for these processes. For example, the measurement of the CP violation in radiative D<sup>0</sup> decays to vector mesons at Belle is consistent with no CP violation [5]. But the sensitivity of the measurement does not reach standard model prediction because statistical uncertainty dominates the measurement's precision.

To improve sensitivity to effects of physics beyond the standard model, we designed an upgrade to the Belle experiment, the Belle II. The Belle II has the goal to increase data set

by factor 50 and improve sensitivity by factor 10. The goal will be achieved by increasing luminosity of the accelerator by factor 40 and improvements in the detectors.

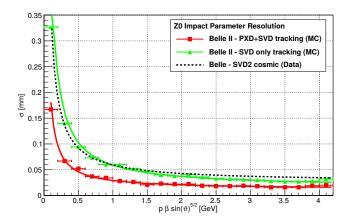

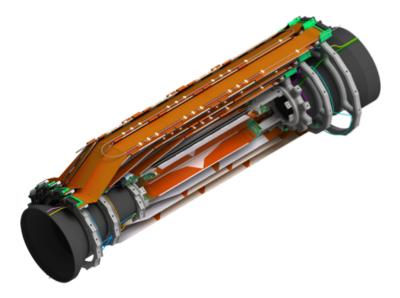

The upgrade of the experiment adds a new pixel detector as the innermost subdetector. The detector will increase the impact parameter resolution of primary vertices. This is needed to compensate lower Lorentz boost of the collision products due to decreased beam energy asymmetry in the upgraded than in Belle. Another task of the detector is the reconstruction of low-momentum pion tracks. The low-momentum pions, which are commonly produced in the  $D^*$  decays, add an important discrimination parameter for selection of charmed meson.

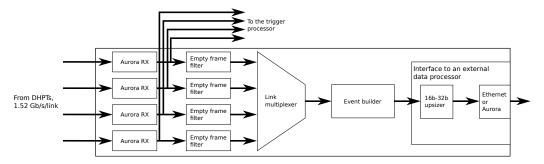

As the innermost subdetector, the pixel detector is most sensitive for the beam background. High granularity of the detector combined with the long integration time results in high data rate of 20 GB/s. High data rate requirement reflects in the design of the data read-out system of the detector.

The second part of the thesis describes the development of the read-out system for the pixel detector of the Belle II experiment. The detector's design places non-trivial requirements for the read-out system. The system must

- synchronize and operate detector modules,

- sustain high data rates,

- process data in real time,

- configure and monitor front-end electronics.

All these requirements are addressed in the system design.

The thesis has following structure. The first part of the thesis describes the measurement of the branching fraction for the decay  $D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0$ . Next chapter describes the source of CP violation in the standard model. Chapter three describes a way for measuring a non-standard model contributions to CP violation in charm decays. Chapter four introduces the Belle experiment where the measurement is done. Chapter five describes the measurement performed using the Belle data sample.

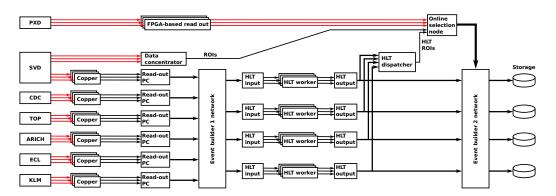

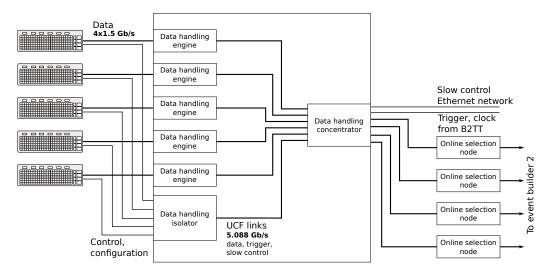

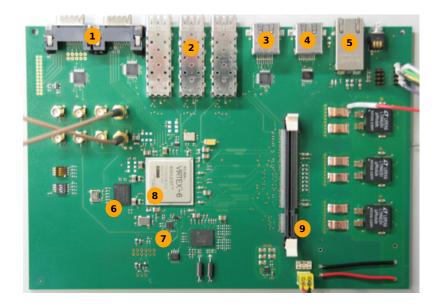

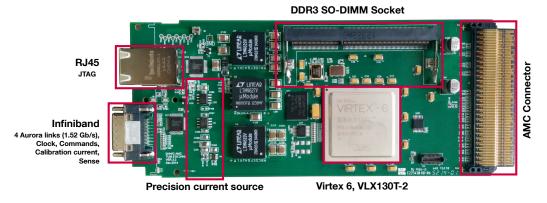

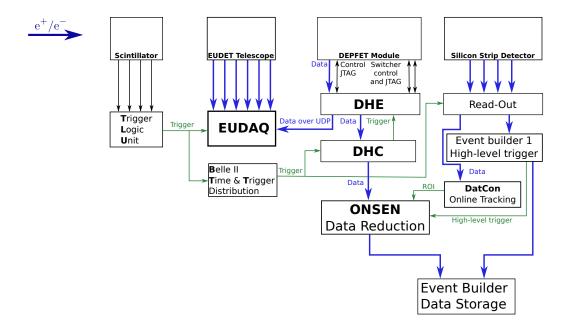

The second part of the thesis describes the development of the read-out system for the pixel detector. Chapter six describes the design of the Belle II experiment. Chapter seven describes the vertex detector which consists of the silicon strip and pixel detector. Chapter eight describes the design of the read-out system of the pixel detector. Chapter nine gives the examples of the system use in different setups.

# Chapter 2.

## The Standard Model and the CP Violation

## 2.1. Discrete Space-Time Symmetries in the Standard Model

Symmetries describe how interactions behave under transformations of system's parameters. Discrete symmetries are a subset of symmetries that mirrors parameters of the system. Two discrete symmetries, the charge conjugation symmetry **C** and the parity symmetry **P**, are important for studying standard model predictions for behavior of particles and antiparticles.

Charge conjugation symmetry transforms particle to its antiparticle. Parity symmetry transforms a particle's handedness: a left-handed particle becomes a right-handed particle and vice-versa. A combination of charge conjugation and parity symmetries, the **CP**, transforms a left-handed particle to a right-handed antiparticle and vice versa.

Three interactions in the standard model behave differently under these transformations. The strong and electromagnetic interactions are invariant under  $\mathbb{C}$ ,  $\mathbb{P}$ , and  $\mathbb{C}\mathbb{P}$  symmetries. We can express this through the decay rates  $\Gamma_{L,R}$  for particles and  $\overline{\Gamma}_{L,R}$  for antiparticles with the given handedness:

$$\Gamma_L = \Gamma_R = \overline{\Gamma}_L = \overline{\Gamma}_R \tag{2.1}$$

The invariance of the interaction is measured as asymmetries between two states:

$$A = \frac{\Gamma_1 - \Gamma_2}{\Gamma_1 + \Gamma_2} \tag{2.2}$$

For strong and electromagnetic interactions these asymmetries wanish

$$\frac{\Gamma_L - \Gamma_R}{\Gamma_L + \Gamma_R} = \frac{\Gamma_L - \overline{\Gamma}_L}{\Gamma_L + \overline{\Gamma}_L} = \frac{\Gamma_L - \overline{\Gamma}_R}{\Gamma_L + \overline{\Gamma}_R} = 0.$$

(2.3)

Bosons of the weak force interact only with left-handed particles and right-handed antiparticles. This maximally violates charge conjugation and parity symmetries

$$\underbrace{\frac{\Gamma_L - \overline{Y}_R}{\Gamma_L + \overline{Y}_R}}_{A_P} = \underbrace{\frac{\Gamma_L - \overline{\overline{Y}}_L}{\Gamma_L + \overline{\overline{Y}}_L}}_{A_C} = 1,$$

(2.4)

but nearly conserves CP symmetry

$$A_{CP} = \left| \frac{\Gamma_L - \overline{\Gamma}_R}{\Gamma_L + \overline{\Gamma}_R} \right| = 10^{-3} \text{ to } 10^{-1}.$$

(2.5)

Study of CP asymmetry lead to the discovery of the CKM matrix which transforms CP eigenstates into the mass eigenstates. This chapter reviews measurements that lead to discovery of CP violation and introduce CP violation in the framework of the CKM theory.

### 2.1.1. Parity Symmetry Violation

The parity operator mirrors spacial coordinates of the system. In 1956, Wu, using a method proposed by Lee and Yang [6], showed that weak force violates parity [7]. Wu and her colleagues studied  $\beta$ -decay of polarized Co<sup>60</sup> nuclei:

$$\text{Co}^{60} \to \text{Ni}^{60} + \text{e}^- + \overline{V}_{\text{e}} + 2\gamma$$

(2.6)

Since electron has positive parity, a reflection of the system should not change its angular distribution. The spin of the Co nucleus, which was aligned to an external magnetic field, provided a reference frame for the measurement. The experiment monitored the rate of the electrons parallel and antiparallel to the spin of the Co nucleus decay and showed that mirroring the reference frame changes the decay rate. This proved that the weak force violates parity symmetry.

### 2.1.2. Charge Conjugation Symmetry Violation

The charge conjugation operator mirrors all charges of a particle, turning it into its antiparticle. In 1957, Garwin, Lederman, and Weinrich showed that the weak force violates **C** symmetry [8]. They measured the angular distributions of electrons and positrons produced in muon and antimuon decays and calculated the helicity for electrons and positrons. If **C** were symmetry of the weak interaction, electrons and positrons would have the same helicity. The experiment showed that electrons and positrons prefer opposite helicities. This proved that the weak interaction violates **C** symmetry.

### 2.2. CP Violation

Discovery that the weak interaction violates **C** and **P** maximally lead to the development of the V-A theory of the weak interaction [9, 10]. The V-A current of the weak interaction theory

$$V - A \equiv \underbrace{\overline{\Psi}\gamma^{\mu}\Psi}_{V} - \underbrace{\overline{\Psi}\gamma^{\mu}\gamma^{5}\Psi}_{A} = \overline{\Psi}\gamma^{\mu}(1 - \gamma^{5})\Psi, \tag{2.7}$$

with  $\overline{\Psi}$  is an antifermion,  $\Psi$  is a fermion, has a left-handed projection operator

$$P_L = (1 - \gamma^5) \tag{2.8}$$

in its structure. This operator projects a fermion field  $\Psi$  to a left-handed fermion field  $\Psi_L$ , and an antifermion field  $\overline{\Psi}$  to a right-handed antifermion field  $\overline{\Psi}_R$ . The structure of the theory predicts that the weak force interacts only with left-handed fermions and right-handed antifermions

$$V - A = \overline{\Psi}_R \gamma^\mu \Psi_L. \tag{2.9}$$

Feynman and Gell-Mann also predicted that a combination of parity transformation and charge conjugation, **CP**, is a conserved symmetry of the weak interaction [10].

Tests of CP symmetry require measurement of the differences in the behavior of matter and antimatter. In 1964, Cronin and Fitch discovered violation of the CP symmetry in decays of neutral kaons. They measured the decay of the pure CP eigenstate into a different CP eigenstate. The effect is caused by tiny difference in the masses of the neutral mesons. In 1972, Kobayashi and Maskawa extended the flavour-mixing matrix discovered by Cabibbo with a third generation of quarks to explain the measured CP violation in the framework of the quantum field theory. This theory is known as the CKM theory<sup>1</sup>. The first quark of the third generation, the beauty quark, was discovered in 1975.

The CKM theory predicts another type of CP violation, direct CP violation, which shows up as an asymmetry in the rates of a decay mode and its CP-conjugate. In 1999, the KTeV experiment at Fermilab and the NA48 experiment at CERN discovered direct CP violation in the decays of neutral kaons — in the same neutral kaon decays in which Cronin and Fitch discovered indirect CP violation. In 2001, the Belle and BaBar experiments confirmed the CKM predictions for direct CP violation in neutral B meson decays.

## 2.3. CP Violating Amplitudes

We can describe CP violation in the amplitude formalism. The amplitude of a decay can be written as

$$A(X \to f) = |A|e^{i\arg A}. (2.10)$$

The amplitude consists of the magnitude |A| and the phase arg(A). The amplitude for the corresponding CP-conjugated decay can be written as

$$\overline{A}(\overline{X} \to \overline{f}) = |\overline{A}|e^{i\arg\overline{A}}.$$

(2.11)

Because their magnitudes must be equal

$$|A| = |\overline{A}|,\tag{2.12}$$

we have freedom to redefine arg(A) as two phases: a CP-even phase  $\delta$  that is not affected under CP transformation and a CP-odd phase  $\phi$  that changes its sign under CP transformation

$$\arg A = \delta + \phi, \tag{2.13}$$

$$\arg \overline{A} = \delta - \phi. \tag{2.14}$$

<sup>&</sup>lt;sup>1</sup>This theory is named after its creators: Cabibbo, Kobayashi, and Maskawa.

Both amplitudes have then the form

$$A(X \to f) = |A|e^{i(\delta + \phi)} \tag{2.15}$$

$$\overline{A}(\overline{X} \to \overline{f}) = |A|e^{i(\delta - \phi)}.$$

(2.16)

If there are several amplitudes which contribute to the same decay, then it is possible to observe the interference of the amplitudes experimentally through the decay rates

$$\Gamma(X \to f) = |A|^2 = |A_1 + A_2|^2$$

(2.17)

$$= |A_1|^2 + |A_2|^2 + |A_1A_2| \left( e^{i((\phi_1 + \delta_1) - (\phi_2 + \delta_2))} + e^{i(-(\phi_1 + \delta_1) + (\phi_2 + \delta_2))} \right) \quad (2.18)$$

$$\Gamma(\overline{X} \to \overline{f}) = |\overline{A}|^2 = |\overline{A}_1 + \overline{A}_2|^2$$

$$= |A_1|^2 + |A_2|^2 + |A_1 A_2| \left( e^{i((-\phi_1 + \delta_1) - (-\phi_2 + \delta_2))} + e^{i(-(-\phi_1 + \delta_1) + (-\phi_2 + \delta_2))} \right).$$

(2.19)

$$(2.20)$$

We can define phase differences as  $\Delta \phi = \phi_1 - \phi_2$ ,  $\Delta \delta = \delta_1 - \delta_2$ , and magnitude ratio  $R = \frac{|A_2|}{|A_1|}$ . Then, we can construct an observable for the strength of the CP violation in a decay channel which can be measured experimentally:

$$A_{CP} = \frac{\Gamma(X \to f) - \Gamma(\overline{X} \to \overline{f})}{\Gamma(X \to f) + \Gamma(\overline{X} \to \overline{f})} = \frac{-2R\sin\Delta\phi\sin\Delta\delta}{1 + R^2 + 2R\cos\Delta\phi\cos\Delta\delta}.$$

(2.21)

The relation shows that CP is violated if and only if

- more than one amplitude contributes to the decay, R > 0,

- the CP-even phase difference  $\Delta \delta$  is not zero,

- the CP-odd phase difference  $\Delta \phi$  is not zero.

CP violation requires CP-odd phase which comes from complex couplings which are complex-conjugated by CP conjugation

$$x = |x|e^{i\phi_x} \xrightarrow{CP} |x|e^{-i\phi_x} = \overline{x}. \tag{2.22}$$

## 2.4. Cabibbo-Kobayashi-Maskawa Matrix

Complex couplings arise as effective couplings between up- and down-type fields in the standard model Lagrangian. We show this by describing the field transformation into the eigenstates of the diagonalized mass matrix in the mass term of the Lagrangian and then transforming the weak term of the Lagrangian to use the eigenstates of the matrix.

In general, the standard model defines two  $3\times3$  mass matrices for up- and down-type fields,  $M_u$  and  $M_d$ , that Yukawa coupling requires for the Higgs mechanism:

$$\mathscr{L}_m = \overline{U}M_\mu UH + \overline{D}M_d DH. \tag{2.23}$$

We can diagonalize the mass matrices with the change-of-basis matrices  $V_u$  and  $V_d$

$$M'_{u} = V_{u}^{\dagger} M_{u} V_{u} = diag(m_{u}, m_{c}, m_{t})$$

(2.24)

$$M'_{d} = V_{d}^{\dagger} M_{d} V_{d} = diag(m_{d}, m_{s}, m_{b}).$$

(2.25)

We then rewrite the mass term as coupling of the eigenstates of the diagonalized matrices

$$\mathcal{L}_{m} = \overline{U}M_{u}UH + \overline{D}M_{d}DH = \underbrace{\overline{U}V_{u}}_{\overline{U}'}M_{u}'\underbrace{V_{u}^{\dagger}U}_{U'}H + \underbrace{\overline{D}V_{d}}_{\overline{D}'}M_{d}'\underbrace{V_{d}^{\dagger}D}_{D'}H = \overline{U}'M_{u}'U'H + \overline{D}'M_{d}'D'H.$$

(2.26)

Now, we transform the weak term of the Lagrangian

$$\mathscr{L}_W \sim \overline{D} \gamma^{\mu} (1 - \gamma_5) U W^{-}_{\mu} \tag{2.27}$$

into eigenstates of the diagonalized mass matrix  $\overline{D}'$  and U'

$$\mathscr{L}_W \sim \overline{\overline{D}} V_d^{\dagger} V_d^{\dagger} \gamma^{\mu} (1 - \gamma_5) V_u \underbrace{V_u^{\dagger} U}_{U'} W_{\mu} = \overline{D}' \gamma^{\mu} (1 - \gamma_5) V_d^{\dagger} V_u U' W_{\mu}. \tag{2.28}$$

The matrix  $V_d^{\dagger}V_u$  is the effective weak coupling of the up- and down-type fields.

In 1963, Nicola Cabibbo used similar approach to describe how to preserve the universality of the coupling in the V–A theory of weak interactions [11]. The mass eigenstates of the d and s quarks<sup>2</sup> are rotated into weak eigenstates d' and s':

$$\begin{pmatrix} d' \\ s' \end{pmatrix} = \begin{pmatrix} \cos\Theta & \sin\Theta \\ -\sin\Theta & \cos\Theta \end{pmatrix} \begin{pmatrix} d \\ s \end{pmatrix}. \tag{2.29}$$

The unitary  $2\times2$  rotation matrix is called the Cabibbo matrix; and  $\Theta$ , the Cabibbo angle. Though the Cabibbo matrix described the weak decays known at that time, it could not describe the CP violation observed by Cronin and Fitch. This is the consequence of Cabibbo matrix not containing complex amplitudes that are needed for CP violation.

In 1972, Kobayashi and Maskawa studied different structures of the weak interaction [12]. They showed that a complex  $n \times n$  matrix has  $n^2$  real parameters. Out of  $n^2$ , (2n - 1) parameters can be absorbed as unphysical quark field phases, which leaves  $(n - 1)^2$  free parameters. By using Cabibbo's approach, we can redefine  $\frac{1}{2}n(n-1)$  as mixing angles. Remaining  $\frac{1}{2}(n-2)(n-1)$  parameters are complex phases.

The Cabibbo's  $2 \times 2$  rotation matrix has one free rotation angle. Rotation by the Cabbibo angle absorbs complex phase of the fermion fields. This means that weak interaction described by a  $2 \times 2$  Cabibbo matrix conserves CP symmetry. Last statement contradicts experimental evidences.

A  $3\times3$  unitary matrix has 4 free parameters of which 3 are independent rotation angles. The remaining free parameter is the complex phase that cannot be rotated away. Presence of a free phase violates CP.

<sup>&</sup>lt;sup>2</sup>Only three quarks – u, d, and s – were known at the time.

The  $3\times3$  unitary matrix

$$\begin{pmatrix} \mathbf{u}' \\ \mathbf{c}' \\ \mathbf{t}' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} \mathbf{d}' \\ \mathbf{s}' \\ \mathbf{b}' \end{pmatrix}$$

(2.30)

described in equation 2.28 is the effective weak coupling matrix  $V_d^{\dagger}V_u$ . This matrix is called the CKM matrix. The rank of the matrix necessitates existence of the third generation of quarks. In 1977, Lederman et al. discovered the first member of the third generation, the beauty quark, in proton-nucleus collisions [13].

CKM matrix is currently the only observed source of CP violation in standard model. We can calculate size of CP violation that arises from effective weak coupling in the CKM theory and compare it with CP asymmetry of the universe.

In 1985, Jarlskog showed that CP violation in the CKM theory comes from a mismatch between up- and down-type matrix [14] with CP asymmetry quantified as

$$A_{univ}^{CP} \approx 2 m_{\rm t}^4 m_{\rm b}^4 m_{\rm c}^2 m_{\rm s}^2 \frac{|J|}{\Lambda^{12}}$$

(2.31)

where J is the Jarlskog invariant,  $\Lambda$  is an energy scale of the process. Jarlskog determinant is a convention-independent measure of CP violation in standard model

$$J = Im(V_{ij}V_{kl}V_{il}^*V_{kj}^*) = (3.172_{-0.098}^{+0.094}) \times 10^{-5} [15].$$

(2.32)

where  $V_{ab}$  are CKM matrix elements. Normalized to the electro-weak scale (100 GeV), the standard model contribution to CP asymmetry of the universe is

$$A_{univ,CKM}^{CP} \approx 10^{-20} [16].$$

(2.33)

Compared to measured CP asymmetry of the universe, given in equation 1.2, the standard model contribution is 10 orders of magnitude below the CP violation which is needed to satisfy Sakharov conditions for the baryogenesys. This comparison shows that we need additional sources of CP violation of the non-CKM structure to explain matter-dominated universe.

# Chapter 3.

# CP Violation in Charm Sector as a Probe for the New Physics

In the previous chapter we estimated the baryon asymmetry using parameters from the standard model. We learned these parameters from measurements of CP violation in weak decays. But CP violation in the standard model is not enough to explain matter-antimatter asymmetry from baryogenesys.

To find missing CP violation, we look for CP violation in decays, where the standard model predicts none. For example, we look in decays of charm quark. It is challenging to estimate absolute magnitude CP violation in charm. Charm mass is in the region, where no perturbative QCD method applies. This makes it not possible to reliably calculate expected CP violation. But we can use other standard model predictions that can be identified by either presence or absence of CP violation. One of these predictions, which I describe in this chapter, is the isospin structure of weak decay. Also, up to now we observed CP violation only in decays of down-type quarks s and b contained in K and B mesons. It would be interesting to measure CP violation in decays of charm quark, because charm quark is the only up-type quark that can have CP violation in hadron decays.

## 3.1. Measurement of CP Violation in Charm

The direct CP violation in the charm sector is expressed by the difference of the CP asymmetries in D mesons decaying to a two-kaon and a two-pion final states

$$\Delta A_{CP} = A_{CP}(D \to KK) - A_{CP}(D \to \pi\pi)$$

(3.1)

The combined fit of the  $\Delta A_{CP}$  parameter to the latest measurements of the CP violation in the charm decays yields no CP violation at 9.3% confidence level [17]. The CP violation from the tree and penguin amplitudes in the singly-Cabibbo suppressed decays is, however, suppressed in the standard model at the level  $10^{-3}$  [18]. Therefore, the current measurement precision allows for an additional non-standard model source of the CP violation.

Grossman et al. [19] propose a test for the subset of the new physics models, which realize the CP-violating  $\Delta I = \frac{3}{2}$  decay amplitudes in the singly-Cabibbo suppressed D decays. For example, the model by Hochberg and Nil predicts a new scalar coupling which

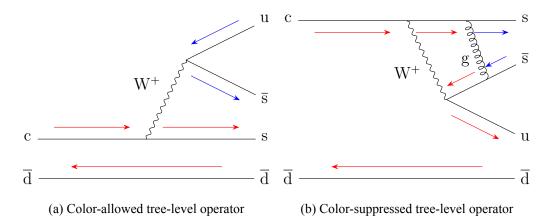

Figure 3.1.: Representative Feynman diagrams for tree-level operators. Arrows show color flow in the diagram

has the  $\Delta I = \frac{3}{2}$  structure [20]. In this analysis we search for the new physics contributions to the CP violation in  $\Delta I = \frac{3}{2}$  decay amplitude in the singly-Cabibbo suppressed decays

$$D^+ \to K^* \overline{K}^* \pi. \tag{3.2}$$

This section shows why the  $\Delta I = \frac{3}{2}$  decay amplitude can only be realized by the physics outside of the standard model based on reference [19].

I will focus on the  $\Delta C = 1$  decays in this thesis. These are decays of charm meson in the initial state into a flavourless final state. The effective Hamiltonian of the decay is

$$H_{\text{eff}} = \frac{G_{\text{F}}}{\sqrt{2}} \left( \sum_{p=\text{d.s}} V_{\text{c}p}^* V_{\text{u}p} (C_1 Q_1^p + C_2 Q_2^p) - V_{\text{cb}}^* V_{\text{ub}} \sum_{i=3}^{6} C_i Q_i + C_{8g} Q_{8g} \right) + h.c.$$

(3.3)

where  $G_F$  is the Fermi constant,  $C_i$  are Wilson coefficients and  $Q_i$  are effective field operators [21].

#### 3.1.1. Tree-Level Operators

There are two types of tree-level operators in the Hamiltonian: a color-allowed operators  $Q_1$ , and a color-suppressed operators  $Q_2$

$$Q_1^p = (\overline{p}_{\alpha} c_{\alpha})_{V-A} (\overline{u}_{\beta} p_{\beta})_{V-A}, \tag{3.4}$$

$$Q_2^p = (\overline{p}_{\alpha} c_{\beta})_{V-A} (\overline{u}_{\beta} p_{\alpha})_{V-A}$$

(3.5)

where  $\alpha, \beta$  is summation over quark colors and p = d,s. The operators describe decay of charm to down-type quarks d and s. Figure 3.1 shows representative Feynman diagrams for a color-allowed and a color-suppressed tree operators. Diagrams show that different colors of  $\overline{s}u$  need a gluon that causes  $\alpha_s$  suppression in the leading order for the

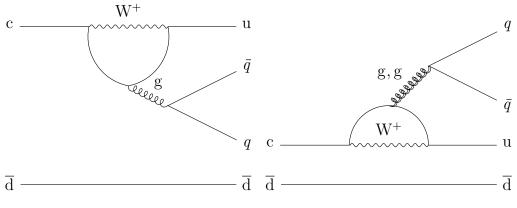

(a) Color-allowed QCD penguin operator

(b) Color-suppressed QCD penguin operator

Figure 3.2.: Representative Feynman diagrams for QCD penguin operators

color-suppressed operator, while the colors of  $\bar{s}u$  are free for the color-allowed operator. Therefore, the color-allowed operator is enhanced by number of colors.

We can calculate the isospin structure of the operator using isospin decomposition. In this parametrization (u, d),  $(\overline{d}, -\overline{u})$ ,  $(D^+, D^0)$ ,  $(K^{*+}, K^{*0})$ ,  $(\overline{K}^{*0}, K^{*-})$  form isospin doublets, (c) forms an isospin singlet, and  $(\pi^+, \pi^0, \pi^-)$  form an isospin triplet. Operators have isospin structure

$$\sum_{p=d,s}\sum_{i=1,2}Q_{i}^{p}:\left|\frac{1}{2},-\frac{1}{2}\right\rangle_{\mathbf{d}}\otimes\left|0\right\rangle_{\mathbf{c}}\otimes\left|\frac{1}{2},\frac{1}{2}\right\rangle_{\mathbf{u}}\otimes\left|\frac{1}{2},\frac{1}{2}\right\rangle_{\overline{\mathbf{d}}}+\left|0\right\rangle_{\overline{\mathbf{s}}}\otimes\left|0\right\rangle_{\mathbf{c}}\otimes\left|\frac{1}{2},\frac{1}{2}\right\rangle_{\mathbf{u}}\otimes\left|0\right\rangle_{\mathbf{s}}= (3.6)$$

$$\left(1+\sqrt{\frac{2}{3}}\right)\left|\frac{1}{2},\frac{1}{2}\right\rangle+\sqrt{\frac{1}{3}}\left|\frac{3}{2},\frac{1}{2}\right\rangle,\tag{3.7}$$

where ket notation  $|I,I_3\rangle$  contains total isospin I and third component of the isospin  $I_3$ . The decomposition shows that both tree-level operators have isospin structure  $\Delta I = \frac{1}{2}$  and  $\Delta I = \frac{3}{2}$ .

#### 3.1.2. Penguin Operators

The standard model penguin operators are

$$Q_{3,5} = (\bar{\mathbf{u}}\mathbf{c}) \sum_{q=u,d,s} (\bar{q}q)_{V \neq A},$$

(3.8)

$$Q_{4,6} = (\overline{\mathbf{u}}_{\alpha} \mathbf{c}_{\beta}) \sum_{q=\mathbf{u}, \mathbf{d}, \mathbf{s}} (\bar{q}_{\beta} q_{\alpha})_{\mathbf{V} \neq \mathbf{A}}, \tag{3.9}$$

$$Q_{8g} = -\frac{g_s}{8\pi^2} m_c \overline{\mathbf{u}} \, \sigma_{\mu\nu} (1 + \gamma_5) G^{\mu\nu} \mathbf{c}. \tag{3.10}$$

The operators  $Q_{3,5}$  are the color-enhanced QCD penguin operators. The operators  $Q_{4,6}$  are the color-suppressed QCD penguin operators. Figure 3.1 shows representative Feynman diagrams for these operators. Color-suppressed operator produce  $q\bar{q}$  in a color-singlet

state, therefore, additional gluons are needed to couple to  $q\bar{q}$ . This suppresses the color-suppressed relative to the color-enhanced operator.

Penguin operators have isospin structure

$$Q_{3-6}: \left|\frac{1}{2}, \frac{1}{2}\right\rangle_{\mathbf{u}} \otimes \left|0\right\rangle_{\mathbf{c}} \otimes \left(-\left|\frac{1}{2}, \frac{1}{2}\right\rangle_{\mathbf{u}} \otimes \left|\frac{1}{2}, -\frac{1}{2}\right\rangle_{\overline{\mathbf{u}}} + \left|\frac{1}{2}, -\frac{1}{2}\right\rangle_{\mathbf{d}} \otimes \left|\frac{1}{2}, \frac{1}{2}\right\rangle_{\overline{\mathbf{d}}}\right) = \sqrt{2} \left|\frac{1}{2}, \frac{1}{2}\right\rangle$$

$$(3.11)$$

that only contains isospin transitions  $\Delta I = \frac{1}{2}$ . The operator  $Q_{8g}$  is the magnetic penguin operator. It has isospin structure

$$Q_{8g}: \left| \frac{1}{2}, \frac{1}{2} \right\rangle_{\mathbf{n}} \otimes |0\rangle_{\mathbf{c}} = \left| \frac{1}{2}, \frac{1}{2} \right\rangle \tag{3.12}$$

that also only contains isospin transitions  $\Delta I = \frac{1}{2}$ .

The fact that all standard model penguin operators have isospin structure  $\Delta I = \frac{1}{2}$  implies that only tree-level amplitudes have  $\Delta I = \frac{1}{2}$  transitions in charm decays.

## 3.1.3. CP Violation in $\Delta I = \frac{3}{2}$ Amplitudes

Grossman et al. used isospin decomposition to construct a pure  $\Delta I = \frac{3}{2}$  amplitude from the amplitudes in a singly-Cabibbo suppressed D<sup>+</sup> decay [19]. We begin with calculating isospin structure of the final states. The decomposition of the final states as eigenstates of isospin is

$$\left|\mathbf{K}^{*+}\overline{\mathbf{K}}^{*0}\boldsymbol{\pi}^{0}\right\rangle = \left|\frac{1}{2},\frac{1}{2}\right\rangle \otimes \left|\frac{1}{2},\frac{1}{2}\right\rangle \otimes \left|1,0\right\rangle \tag{3.13}$$

$$= \sqrt{\frac{1}{2}} |2,1;1\rangle + \sqrt{\frac{1}{2}} |1,1;1\rangle \tag{3.14}$$

$$\left|\mathbf{K}^{*+}\mathbf{K}^{*-}\boldsymbol{\pi}^{+}\right\rangle = \left|\frac{1}{2},\frac{1}{2}\right\rangle \otimes \left|\frac{1}{2},-\frac{1}{2}\right\rangle \otimes \left|1,1\right\rangle \tag{3.15}$$

$$= \frac{1}{2} |2,1;1\rangle - \frac{1}{2} |1,1;1\rangle + \sqrt{\frac{1}{2}} |1,1;0\rangle \tag{3.16}$$

$$\left|\mathbf{K}^{*0}\overline{\mathbf{K}}^{*0}\boldsymbol{\pi}^{+}\right\rangle = \left|\frac{1}{2}, -\frac{1}{2}\right\rangle \otimes \left|\frac{1}{2}, \frac{1}{2}\right\rangle \otimes \left|1, 1\right\rangle \tag{3.17}$$

$$= \frac{1}{2} |2,1;1\rangle - \frac{1}{2} |1,1;1\rangle - \sqrt{\frac{1}{2}} |1,1;0\rangle, \qquad (3.18)$$

(3.19)

where ket notation  $\left|I,I_3;I_{K^*\overline{K}^*}\right\rangle$  contains total isospin I, third component of the isospin  $I_3$ , and total isospin of the  $K^*\overline{K}^*$  pair  $I_{K^*\overline{K}^*}$ .

Then, we calculate isospin projections of the effective operators  $O_{\frac{1}{2}}$  and  $O_{\frac{3}{2}}$  for isospin transitions  $\Delta I = \frac{1}{2}$  and  $\Delta I = \frac{3}{2}$  in D<sup>+</sup> decay:

$$O_{\frac{1}{2}}\left|\mathbf{D}^{+}\right\rangle = \left|\frac{1}{2}, \frac{1}{2}\right\rangle \otimes \left|\frac{1}{2}, \frac{1}{2}\right\rangle = \left|1, 1\right\rangle,\tag{3.20}$$

$$O_{\frac{3}{2}} | D^{+} \rangle = | \frac{3}{2}, \frac{1}{2} \rangle \otimes | \frac{1}{2}, \frac{1}{2} \rangle = -\frac{1}{2} | 1, 1 \rangle + \frac{\sqrt{3}}{2} | 2, 1 \rangle.$$

(3.21)

Next, we calculate matrix elements for the operators in a basis of total isospin eigenstates separated by total isospin of the  $K^* \overline{K}^*$  pair:

$$\langle 1, 1; 0 | O_{\frac{1}{2}} | D^{+} \rangle \equiv B_{1}', \tag{3.22}$$

$$\langle 1, 1; 0 | O_{\frac{3}{2}} | D^{+} \rangle \equiv -\frac{1}{2} B_{3}',$$

(3.23)

$$\langle 1, 1; 1 | O_{\frac{1}{2}} | D^{+} \rangle \equiv B_{1},$$

(3.24)

$$\langle 1, 1; 1 | O_{\frac{3}{2}} | D^+ \rangle \equiv -\frac{1}{2} B_3,$$

(3.25)

$$\langle 2, 1; 1 | O_{\frac{1}{2}} | D^{+} \rangle \equiv 0,$$

(3.26)

$$\langle 2, 1; 1 | O_{\frac{3}{2}} | D^{+} \rangle \equiv \frac{\sqrt{3}}{2} C_{3}.$$

(3.27)

We combine isospin decomposition of the final states with matrix elements for operators  $O_{\frac{1}{2}}$  and  $O_{\frac{3}{2}}$  to calculate amplitudes for  $D^+$  decay to each final state:

$$A^{+00} \equiv \left\langle \mathbf{K}^{*+} \overline{\mathbf{K}}^{*0} \pi^{0} \middle| O_{\frac{1}{2}} + O_{\frac{3}{2}} \middle| D^{+} \right\rangle = \frac{1}{2} \left( \sqrt{2} B_{1} + \frac{\sqrt{3}}{\sqrt{2}} C_{3} - \frac{1}{\sqrt{2}} B_{3} \right), \tag{3.28}$$

$$A^{+-+} \equiv \left\langle \mathbf{K}^{*+} \mathbf{K}^{*-} \boldsymbol{\pi}^{+} \middle| O_{\frac{1}{2}} + O_{\frac{3}{2}} \middle| \mathbf{D}^{+} \right\rangle = \frac{1}{2} \left( -B_{1} + \sqrt{2}B'_{1} + \frac{\sqrt{3}}{2}C_{3} + \frac{1}{2}B_{3} - \frac{1}{\sqrt{2}}B'_{3} \right), \tag{3.29}$$

$$A^{00+} \equiv \left\langle \mathbf{K}^{*0} \overline{\mathbf{K}}^{*0} \pi^{+} \middle| O_{\frac{1}{2}} + O_{\frac{3}{2}} \middle| \mathbf{D}^{+} \right\rangle = \frac{1}{2} \left( -B_{1} - \sqrt{2}B_{1}' + \frac{\sqrt{3}}{2}C_{3} + \frac{1}{2}B_{3} + \frac{1}{\sqrt{2}}B_{3}' \right). \tag{3.30}$$

By adding the amplitudes we construct a pure  $\Delta I = \frac{3}{2}$  amplitude

$$\sqrt{2}A^{+00} + A^{+-+} + A^{00+} = \sqrt{3}C_3. \tag{3.31}$$

To test standard model, we can measure CP asymmetry in  $C_3$

$$A^{CP}(C_3) = \frac{|C_3|^2 - |\overline{C_3}|^2}{|C_3|^2 + |\overline{C_3}|^2} = \frac{\left|\sqrt{2}A^{+00} + A^{+-+} + A^{00+}\right|^2 - \left|\sqrt{2}A^{-00} + \overline{A}^{-+-} + \overline{A}^{00-}\right|^2}{\left|\sqrt{2}A^{+00} + A^{+-+} + A^{00+}\right|^2 + \left|\sqrt{2}\overline{A}^{-00} + \overline{A}^{-+-} + \overline{A}^{00-}\right|^2}.$$

(3.32)

Because standard model only allows  $\Delta I = \frac{3}{2}$  transitions in tree amplitudes, CP asymmetry will always cancel for this eigenstate in standard model. Any non-zero CP violation in this eigenstate is a clear sign for physics beyond the standard model.

To have non-zero CP violation, the interference terms in

$$\left|\sqrt{2}A^{+00} + A^{+-+} + A^{00+}\right|^{2} = 2\left|A^{+00}\right|^{2} + \left|A^{+-+}\right| + \left|A^{00+}\right|^{2} + 2\left|A^{+00}\right| \left|A^{+-+}\right| \left|\cos\Delta\delta_{+-+}^{+00}\right|$$

(3.33)

$$+2\left|A^{+00}\right|\left|A^{00+}\right|\cos\Delta\delta_{00+}^{+00}+2\left|A^{+-+}\right|\left|A^{00+}\right|\cos\Delta\delta_{00+}^{+-+},\tag{3.34}$$

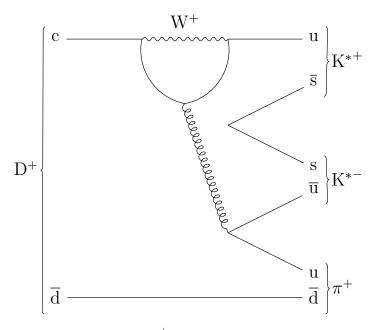

Figure 3.3.: One of the possible D<sup>+</sup> decay amplitude in the channel of interest

where  $\Delta \delta_{+-+}^{+00}$ ,  $\Delta \delta_{00+}^{+00}$ ,  $\Delta \delta_{00+}^{+-+}$  are CP-even phase differences between amplitudes, must not vanish.

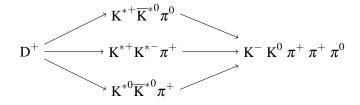

# 3.2. Decay $D^+ \to K^*K^*\pi$

One of the decay channels proposed by Grossman et al. in [19] for the search of the  $\Delta I = \frac{3}{2}$  decay amplitude is the channel

$$D^+ \to K^*K^*\pi.$$

This channel has a common final state for the decay modes  $K^{*+}\overline{K}^{*0}\pi^0$ ,  $K^{*+}K^{*-}\pi^+$ , and  $K^{*0}\overline{K}^{*0}\pi^+$ :

Figure 3.3 shows one of the possible diagram. This channel has the advantage that the common final state allows us to reconstruct relative phases of the decay amplitudes by analysing their overlap in the phase space of the five-body final state.

The decay  $D^+ \to K^- K^0_S \pi^+ \pi^+ \pi^0~$  offers a practical way of measuring new physics contributions on the theory side. However, this decay has never been observed before. Therefore, in this work I will focus on measuring the branching fraction of this decay at Belle experiment.

To estimate expected branching fraction we consider decay mode  $D^+ \to K^- K_S^0 \pi^+ \pi^+$  with branching fraction (0.234±0.018)%. We expect that additional  $\pi^0$  would only affect the available phase space of the decay. We estimate that branching fractions of the decay would have similar ratio as the ratio of their phase space volume V per particle

$$\frac{BF(D^{+} \to K^{-}K_{S}^{0}\pi^{+}\pi^{+}\pi^{0})}{BF(D^{+} \to K^{-}K_{S}^{0}\pi^{+}\pi^{+})} \sim \frac{\sqrt[5]{V_{D^{+} \to K^{-}K_{S}^{0}\pi^{+}\pi^{+}\pi^{0}}}}{\sqrt[4]{V_{D^{+} \to K^{-}K_{S}^{0}\pi^{+}\pi^{+}}}} \approx 0.55.$$

(3.35)

Alternatively, we compare branching fractions for two  $D^0$  decays that have similar kinematics

$$\frac{BF(D^0 \to K^- K^+ \pi^+ \pi^- \pi^0)}{BF(D^0 \to K^- K^+ \pi^+ \pi^-)} = \frac{(3.2 \pm 2.0) \%}{(2.4 \pm 0.1) \%} = 1.3 \pm 0.8.$$

(3.36)

Precision of the branching fraction measurement for decay  $D^0 \to K^-K^+\pi^+\pi^-\pi^0$  leaves room for suppression by one order of magnitude. Therefore, we expect branching fraction of the decay  $D^+ \to K^-K^0_S\pi^+\pi^+\pi^0$  to be in the order of  $10^{-4}$ .

# Chapter 4.

# Belle Experiment

The Belle experiment was a solid angle spectrometer at the KEKB B factory at the High Energy Accelerator Research Organization KEK  $^1$ , in Tsukuba, Japan. KEKB is an electron-positron collider that operates at and near the  $\Upsilon(4S)$  resonance. The  $\Upsilon(4S)$  resonance is the first  $b\bar{b}$  resonance above the threshold to decay to a pair of  $B-\overline{B}$  mesons, to which it decays 96% of the time. A main goal of the Belle experiment was to study the properties of the b quark.

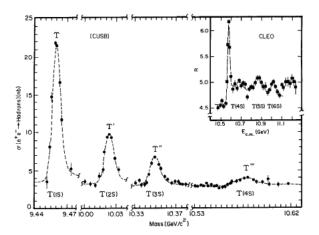

Figure 4.1 shows the cross section for inclusive hadron production in  $e^-e^+$  collisions. There are resonant bottomonium states  $\Upsilon$ , where  $\Upsilon(4S)$  is the first resonance that can produce  $B-\overline{B}$  mesons. The  $\Upsilon(4S)$  resonance is above a flatter source of nonresonant cross-section that is the source for  $q\bar{q}$  production. The cross section for charm production is

$$\sigma(e^-e^+ \to c\bar{c})_{\Upsilon(4S)} = 1.3 nb$$

where a D meson is produced 90 % of the time. This is comparable with beauty production at the  $\Upsilon(4S)$  resonance

$$\sigma(e^-e^+ \to b\overline{b})_{\Upsilon(4S)} = 1.1 nb.$$

Therefore, the KEKB produces comparable number of the D mesons, which we use to study CP violation in the  $D^+$  meson decays.

## 4.1. KEKB B Factory

The KEKB B factory is asymmetric in energy. It consists of a linear accelerator and two accelerator rings. Electrons and positrons are produced in the linear accelerator and accelerated to 3 GeV. Then, they are injected into the ring accelerators. The rings have the circumference 3016 m and share the same tunnel. One ring accelerates electrons to 8 GeV. The other ring accelerates positrons to 3.5 GeV.

The rings intersect at an interaction point where the beams collide. The asymmetric beam energies give the collision products a Lorentz boost in the direction of the electrons. The Lorentz boost is important for precise measurement of decay times of the collision products.

During 10 years of operation, KEKB delivered  $1 \text{ ab}^{-1}$  integrated luminosity. This corresponds to  $7.7 \times 10^8 \text{ BB}$  pairs and a comparable number of D mesons.

<sup>&</sup>lt;sup>1</sup>高エネルギー加速器研究機構 [Kō Enerugī Kasokuki Kenkyū Kikō] – High Energy Accelerator Research Organization

Figure 4.1.: Cross-section for inclusive hadron production by e<sup>-</sup>e<sup>+</sup> annihilation in the energy region of the upsilon system [22].

## 4.2. Belle Detector

The Belle detector is an almost- $4\pi$ , general-purpose spectrometer that covers the polar angle from  $17^{\circ}$  to  $150^{\circ}$  around the interaction region of KEKB. The high acceptance allows us to reconstruct full decay chain of D mesons by detecting their decay products.

The detector has a cylindrical coordinate system with longitudinal coordinate z, which is aligned with positron beam, radial coordinate r, and azimuth angle  $\phi$ . The direction of the z-axis is in electron flight direction. The origin of the coordinate system is at the interaction point. The detector consists of the central barrel region and two end cap regions: forward end cap in the positive-z region and backward end cap in the negative-z region.

Figure 4.2 shows the layout of the Belle experiment. Subdetectors cover interaction point cylindrically. A particle passes silicon vertex detector, central drift chamber, time-of-flight detector, electromagnetic calorimeter, and  $K_L^0$  and muon detector in the barrel region. In end cap region, a particle passes silica aerogel counter detector in the forward end cap, electromagnetic calorimeter, and  $K_L^0$  and muon detector in both forward and backward end caps. The extreme forward calorimeter, which is installed on the front face of the compensation magnet's cryostat, measures luminosity by measuring rate of the electron-positron scattering. A full technical description of the detector is available in [23].

#### 4.2.1. Silicon Vertex detector

The silicon vertex detector, with fine spacial resolution, measures position of the primary decay vertices. The hits in the silicon vertex detector are also used in track reconstruction.

The detector is comprised of double-sided silicon strips using CMOS technology. One side of the detector contains  $P^+$  strips, the other side contains  $N^+$  strips that are perpendicular to  $P^+$  strips. Charged particles, which cross the detector, produce electron-hole

Figure 4.2.: Layout of the Belle detector

pair in depleted silicon bulk. Electrons and holes drifting to opposite sides of the detector produce electric signal in the strips. We reconstruct position of charged particles by correlating signals from P<sup>+</sup> and N<sup>+</sup> strips in time.

Two silicon vertex detectors existed in the Belle experiment. The first detector, SVD1, consisted of 3 detector layers and operated from the start of the experiment until October 2003 [23]. The detector suffered from radiation damage, which decreased the signal-to-noise ratio by 30%. So the detector was replaced by one with radiation-hard components. This second detector, SVD2, consists of 4 detector layers and operated until the end of the experiment [24]. It covered a slightly larger polar angle and, due to a faster shaper, reduced the dead time — from 6.4% in SVD1 to 1% in SVD2. The upgrade lead to the improvement of the vertex location resolution.

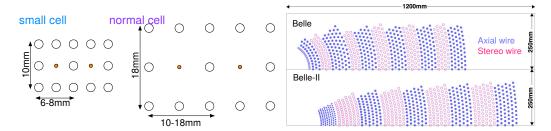

#### 4.2.2. Central Drift Chamber

The central drift chamber is used to determine momentum of a particle by measuring a track over a long leverarm [23]. The specific energy loss of a track in the drift chamber gives information about its particle type.

The central drift chamber consists of 13 cylindrical layers and is filled with a heliumethane mixture. Charged particles ionize gas in the chamber. Ion then drift towards a sensitive wire where they induce electric signal. We reconstruct a two-dimensional projection of the track by combining hits that are close in space and in time. Two types of layers are installed alternatively: layers parallel to the z axis and layers at a small angle to the z axis. Timing coincidence of hits in these layers gives information about the zcoordinate of the track in addition to the r and  $\phi$  coordinates. The curvature of the track in constant magnetic field allows us to measure momentum of the particle.

#### 4.2.3. Particle Identification Detectors

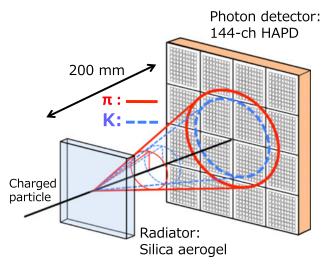

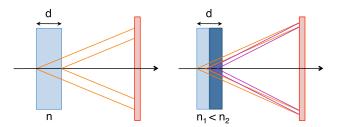

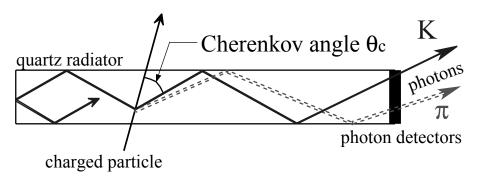

The primary goal of the silica aerogel Cherenkov counter and the time-of-flight detectors is to precisely identify species of the charged tracks.

The aerogel ring-imaging Cherenkov detector detects Cherenkov light, emitted by a charged track, in the aerogel medium [23]. This subdetector covers the barrel and the forward end-cap regions. The light yield measured by the detector is proportional to the shape of the Cherenkov light cone, which depends on the particle's mass and momentum. We can calculate mass of a particle using the light yield and momentum measured via the central drift chamber.

The time-of-flight detector covers the barrel region. It uses two layers of fast scintillator counters to measure the time a particle needs to travel the distance between the layers. With velocity and momentum, we can calculate mass of the particle and determine its species.

### 4.2.4. Electromagnetic Calorimeter

The electromagnetic calorimeter measures energy deposited in the detector by the particle. The calorimeter consists of the 8736 Cs(Tl)I crystals which cover full acceptance range of the Belle detector. The 30 cm deep Cs(Tl)I crystals used in Belle cover 16.2 units of radiation length. This allows them to fully absorb most electromagnetically interacting particles.

High segmentation of the calorimeter, while increasing the complexity and reducing the efficiency of the detector, is optimized for reconstruction of the photons. Photons leave very compact shower in the crystal. Typically, a photon candidate leaves more than 80 % of its energy in one crystal. To account for the case when the photon traverses more than one crystal, this condition is relaxed. The condition which we use in Belle considers the ratio of energies which the photon leaves in a central  $3\times3$  cluster and in a central  $5\times5$  cluster. We require this ratio to be

$$E9oE25 = \frac{E(3 \times 3)}{E(5 \times 5)} > 0.85$$

to select good photon candidates.

Information from particle identification detectors, specific energy loss and momentum measured in the central drift chamber, and energy, deposited in the electromagnetic calorimeter, flow into calculation of the likelihood ratios for a track hypothesis. I use the likelihood ratios in the reconstruction software to quantify the probability of a track being a specific particle.

# Chapter 5.

Search for the Decay

$$D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0$$

# 5.1. Analysis Overview

To calculate branching fraction of a decay channel, we must know three quantities:

- signal yield, obtained from the fit to reconstructed data,

- · reconstruction efficiency, and

- number of D mesons in data sample.

But because D mesons are not resonantly produced at Belle, we cannot estimate their number in the data sample with sufficient precision. Therefore, I measured branching fraction relative to a well-known channel  $D^+ \to K^- K_S^0 \pi^+ \pi^+$  with branching fraction

BF(D<sup>+</sup>

$$\to$$

K<sup>-</sup>K<sub>S</sub><sup>0</sup> $\pi$ <sup>+</sup> $\pi$ <sup>+</sup>) = (0.234 ± 0.018) %. (5.1)

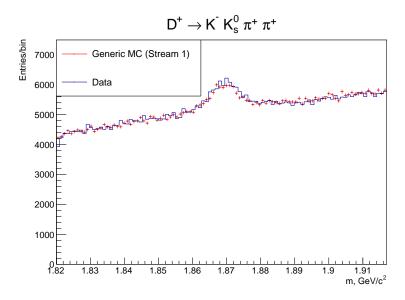

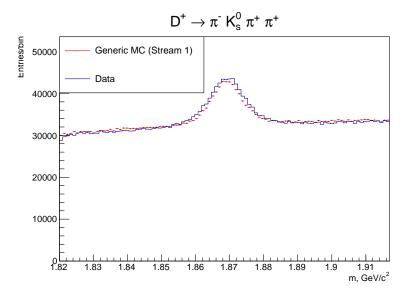

As a cross-check, I reconstructed another four-particle D decay channel  $D^+ \to \pi^- K_S^0 \pi^+ \pi^+$ . The normalizing channel has the same number and same types of charged tracks as the 5-particle decay mode, which I want to measure. This brings the advantage that systematic uncertainties of the measurement associated with measuring charged tracks cancel in the branching fraction calculation.

The analysis is performed on all decay channels in the same manner. First, I simulate all decay channels using Monte Carlo simulation. Events in the simulation are distributed according to available phase space. Then, I select events from phase space simulated data, signal Monte Carlo, and from full experiment simulation, generic Monte Carlo, using loose selection criteria. With these events, I train a boosted decision tree classifier that is used to obtain final data sample. I use final data sample to calculate efficiencies and define signal and background shapes for all decay channels. The efficiencies are used in the normalized branching fraction measurement

$$Br(channel) = \left(\frac{yield_{channel}}{\varepsilon_{channel}} / \frac{yield_{norm}}{\varepsilon_{norm}}\right) \times Br(norm). \tag{5.2}$$

The final data sample is used to study our sensitivity to the signal. I first fit invariant mass of the simulated signal and background events independently to create models for their shape. Then, I add both models and fit the final data sample to obtain the signal yield. In addition, I explore sensitivity of the measurement by fitting data samples that contain different signal fractions.

## 5.2. Monte Carlo Simulations

To study selection efficiencies and signal shapes, I simulate signal decays using Monte Carlo technique. This simulation is called signal MC. For the 5-particle decay channel, I simulate a prompt  $D^+$  decay, where  $D^+$  immediately decays to final-state particles, and three subchannels, where  $D^+$  first decays to  $K^*K^*\pi$  which then decays to final-state particles. For every channel, including  $K^*K^*\pi$  sub-channels, I generate  $10^7$  events with Evt-GEN with kinematics of the decays distributed according to available phase space [25]. Detector response is simulated with GEANT3 software [26].

I study background shapes and composition on the full experiment simulation, called generic MC. I reconstruct three independent data sets and use one data set for preparing event selection and two other data sets for verification of the event selection on the background distribution.

#### 5.3. Event Selection

I start decay reconstruction with event selection using loose selection criteria. The event selection algorithms focus on rejecting as many of background events as possible to reduce data size. I use same selection criteria in all decay channels. Due to common selection criteria, charged tracks have same kinematic distribution, which leads to cancellation of systematic uncertainties in normalizing branching fraction. The selection algorithm for different decay channels differ only in number and types of the reconstructed final-state particles.

Table 5.1 lists cuts used in event selection. First, I select events based on their 2nd Fox-Wolfram moment  $R_2$  defined as

$$H_n = \sum_{i,j=1}^{N} \frac{|\vec{p}_i| |\vec{p}_j|}{s} P_n(\cos\Omega_{ij}), \tag{5.3}$$

$$R_2 = \frac{H_2}{H_0} \tag{5.4}$$

with  $\vec{p}_{i,j}$  are four-momenta of the particles,  $P_2$  is the Legendre polynomial of degree 2, and  $\Omega_{ij}$  is the opening angle between particles [27]. The 2nd Fox-Wolfram moment discriminates event by their sphericity. I discard events with the normalized moment below 0.1 to remove jet-like events.

Neutral pions are reconstructed from two good photon candidates with E9oE25 ratio, described in section 4.2.4, greater than 0.85. I require  $\chi^2$  of the mass constrained fit to a pair photons to be smaller than 16 and momentum of  $\pi^0$  to be greater than 0.22 GeV.

I reconstruct  $K_S^0$  from a  $\pi^+\pi^-$  pair using the standard cut of the nisKsFinder algorithm to select good kaons [28]. NisKsFinder is a machine learning algorithm that uses 13 kinematic parameters of the  $K_S^0$  candidate and its daughter  $\pi^+\pi^-$  to select candidates with high efficiency.

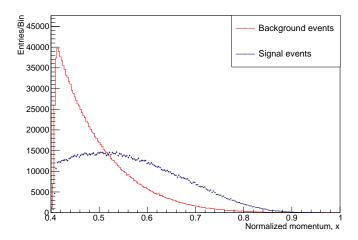

Figure 5.1.: Distribution of the normalized momentum for signal and background events in the  $D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0$  mode.

I select charged tracks using likelihood values, calculated by particle identification for every track and every mass hypothesis. To separate pions from kaons, I use the likelihood ratio  $L_{\rm K/\pi}$  that is calculated from probabilities of a track for being a pion  $L_{\pi}$  or a kaon  $L_{\rm K}$

$$L_{K/\pi} = \frac{L_{K}}{L_{K} + L_{\pi}}. (5.5)$$

I additionally require charge tracks to originate from region close to interaction point and to have at least 2 hits in the vertex detector to reject poorly reconstructed tracks.

I combine all particles to a  $D^+$  candidate. I require invariant mass of the  $D^+$  candidate to be limited to a region around nominal  $D^+$  mass. I fit  $D^+$  vertex using all charged tracks of the  $D^+$  candidate [29]. I require that the fit does not fail. This removes many purely combinatorial background events.

The normalized momentum of the D<sup>+</sup> candidate

$$x = \frac{P_D}{\sqrt{\frac{s}{4} - M_D^2}} \tag{5.6}$$

must be greater than 0.4. Figure 5.1 shows normalized distribution of normalized momentum for signal and background events. Background events peak at low value of x, while signal events peak at 0.5. Cutting on 0.4 reduces a large fraction of background events.

#### 5.3.1. Geometric Acceptance and Selection Efficiency

I calculate geometric acceptance and signal selection efficiency by comparing total number of events generated in signal MC with number of detectable events and number of correctly reconstructed events. The number of detectable events is the number of decays

| Parameter                                                                                                          | Selection criteria                            | Comment                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------|--|--|--|

| Events                                                                                                             |                                               |                                            |  |  |  |

| $R_2$                                                                                                              | > 0.1                                         | 2nd Fox-Wolfram moment                     |  |  |  |

|                                                                                                                    | $\pi^0$                                       |                                            |  |  |  |

| $\chi^2_{\pi^0}$                                                                                                   | < 16                                          | $\chi^2$ of the mass fit                   |  |  |  |

| $ \vec{p}_{\pi^0} $                                                                                                | > 0.22 GeV/c                                  |                                            |  |  |  |

| E9oE25, $\gamma$ for $\pi^0$                                                                                       | > 0.85                                        | Energy ratios for daughter photons         |  |  |  |

|                                                                                                                    | Charged tracks                                |                                            |  |  |  |

| $L_e$                                                                                                              | < 0.6                                         | probability of a track being an electron   |  |  |  |

| $L_p$                                                                                                              | < 0.6                                         | probability of a track being a proton      |  |  |  |

| $L_{\mathrm{K}/\pi}$ for $\mathrm{K}^{\pm}$                                                                        | < 0.6                                         |                                            |  |  |  |

| $egin{array}{c} L_p \ L_{	ext{K}/\pi} 	ext{ for } 	ext{K}^\pm \ L_{	ext{K}/\pi} 	ext{ for } \pi^\pm \ \end{array}$ | > 0.6                                         |                                            |  |  |  |

| dr                                                                                                                 | < 10 mm                                       | impact parameter of a track in r direction |  |  |  |

| dz                                                                                                                 | < 15 mm                                       | impact parameter of a track in z direction |  |  |  |

| Number of SVD hits                                                                                                 | > 2 per charged track                         |                                            |  |  |  |

| $D^+$                                                                                                              |                                               |                                            |  |  |  |

| $m_{ m D^+}$                                                                                                       | $(1.8196 < m_{D^+} < 1.9196) \text{ GeV/c}^2$ |                                            |  |  |  |

| X                                                                                                                  | > 0.4                                         | normalized momentum                        |  |  |  |

Table 5.1.: Selection criteria used in the skim module

where all final state-particles of the  $D^+$  decay hit Belle detector. The number of correctly reconstructed events is calculated by matching reconstructed candidates and their daughter particles with MC truth.

I calculate geometric acceptance as a ratio of detectable particles to the total number of events:

$$A = \frac{N_{\text{detectables}}}{N_{\text{total}}}. (5.7)$$

Geometric acceptance is limited by detector geometry and cannot be improved in analysis. I calculate selection efficiency as a ratio of correctly reconstructed candidates to detectable events:

$$\varepsilon_{\rm sel} = \frac{N_{\rm correct}}{N_{\rm detectables}}.$$

(5.8)

I calculate detection efficiency as a product of selection efficiency and geometric acceptance:

$$\varepsilon_{\text{det}} = A \cdot \varepsilon_{\text{sel}}.$$

(5.9)

Table 5.2 lists number of reconstructed events in generic MC. I reconstruct no signal events in the 5-particle channel because this channel has not been measured yet and is not

| Decay                                                               | Number of reconstructed events |           |             |

|---------------------------------------------------------------------|--------------------------------|-----------|-------------|

|                                                                     | Total Signal Background        |           |             |

|                                                                     |                                |           |             |

| $D^+ \to K^- K_S^0 \pi^+ \pi^+ \pi^0$                               | 1'960'396                      | 0         | 1'960'396   |

| $\mathrm{D}^+ \to \mathrm{K}^- \mathrm{K}^0_\mathrm{S} \pi^+ \pi^+$ | 15'104'297                     | 453'042   | 14'651'255  |

| $\mathrm{D}^+ \to \pi^- \mathrm{K}_\mathrm{S}^0 \pi^+ \pi^+$        | 118'150'470                    | 2'609'381 | 115'541'089 |

Table 5.2.: Number of reconstructed events in generic MC

| Decay                                                               | Acceptance, % | $\varepsilon_{ m sel},\%$ | $\varepsilon_{ m det}$ , % |

|---------------------------------------------------------------------|---------------|---------------------------|----------------------------|

| ${\over D^+ 	o K^- K_S^0 \pi^+ \pi^+ \pi^0}$                        | 10.6          | 16.00                     | 2.00 + 0.0056              |

|                                                                     | 18.6          | 16.08                     | $2.99 \pm 0.0056$          |

| $K^{*+}K^{*-}\pi^{+}$                                               | 20            | 17.46                     | $3.50 \pm 0.0120$          |

| $\mathrm{K}^{*+}\overline{\mathrm{K}}^{*0}\pi^0$                    | 17.1          | 12.07                     | $2.07 \pm 0.0090$          |

| ${\rm K}^{*0}\overline{\rm K}^{*0}\pi^+$                            | 19.5          | 17.34                     | $3.39 \pm 0.0120$          |

| $\mathrm{D}^+ \to \mathrm{K}^- \mathrm{K}^0_\mathrm{S} \pi^+ \pi^+$ | 38.9          | 37.7                      | $14.60 \pm 0.0120$         |

| $\mathrm{D}^+  ightarrow \pi^- \mathrm{K}^0_\mathrm{S} \pi^+ \pi^+$ | 37.6          | 42.9                      | $16.10 \pm 0.0130$         |

Table 5.3.: Geometric acceptance and selection efficiencies

a part of generic MC. Therefore, for efficiency calculation I use data from signal MC for all channels.

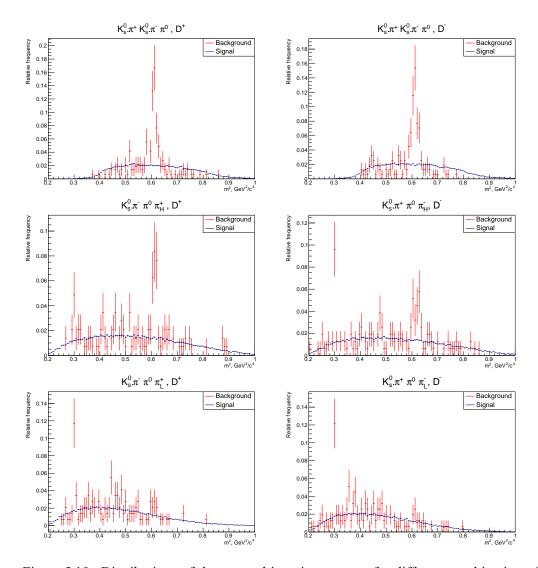

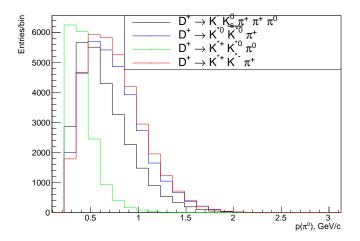

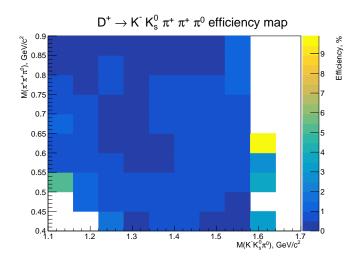

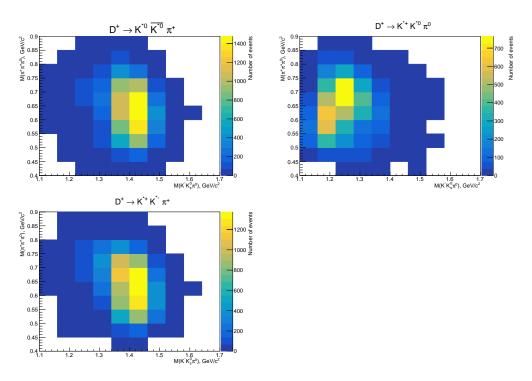

Table 5.3 lists acceptances and efficiencies for all channels. The efficiency of the  $K^{*+}\overline{K}^{*0}\pi^0$  subchannel is significantly lower than the efficiencies of other subchannels. This effect is caused by  $\pi^0$  momentum cut and different momentum distributions of  $\pi^0$  in different subchannels. Section 5.4.6 describes this effect in more details.

#### 5.4. Post-Skim Event Selection

Due to very loose cuts in the skim module, the ratio of signal events to background events at the expected branching fraction  $10^{-4}$  is  $7.5 \cdot 10^{-4}$ . This ratio is too low to measure the signal fraction. Therefore, additional event selection is done on the pre-selected data.

For the final event selection, I train boosted decision trees for background separation, optimize cuts on the kinematic variables, and use best candidate selection to keep a single candidate per event.

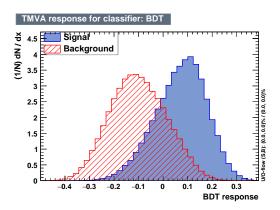

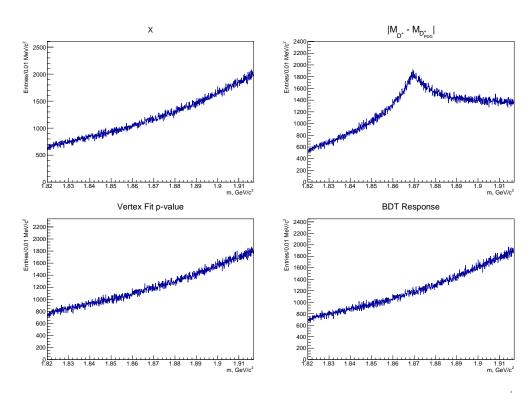

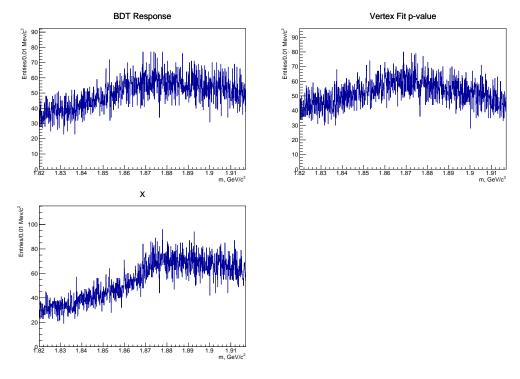

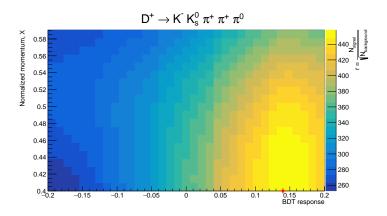

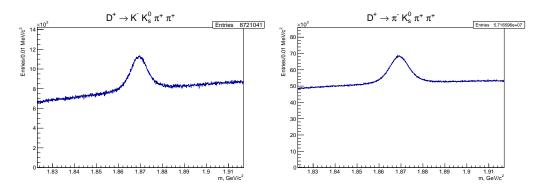

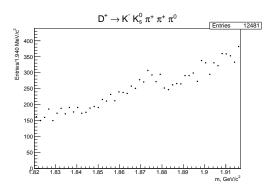

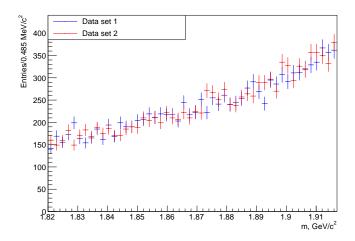

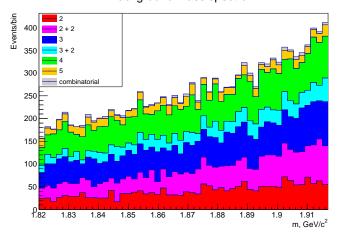

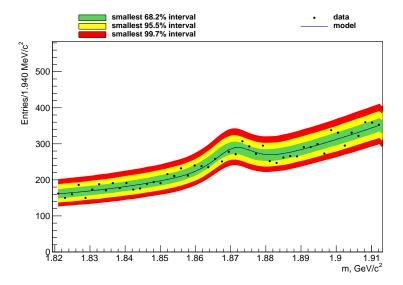

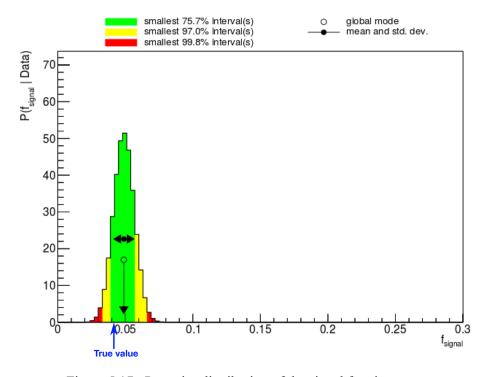

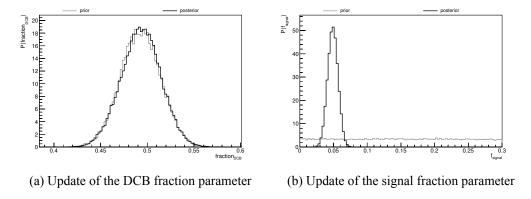

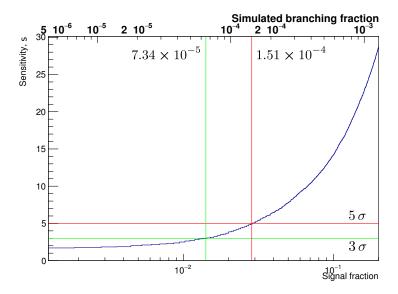

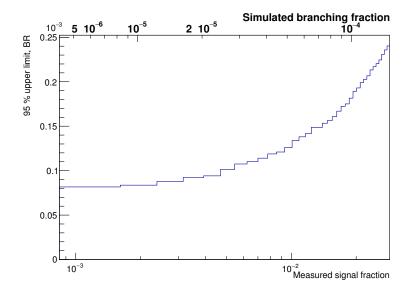

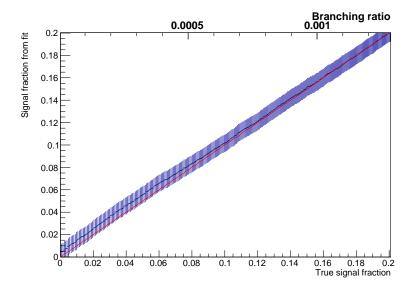

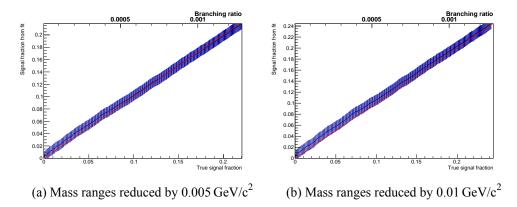

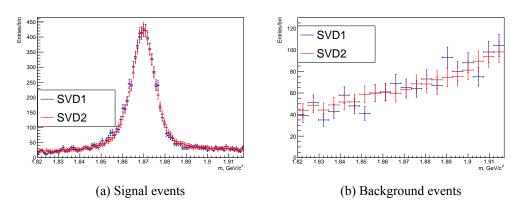

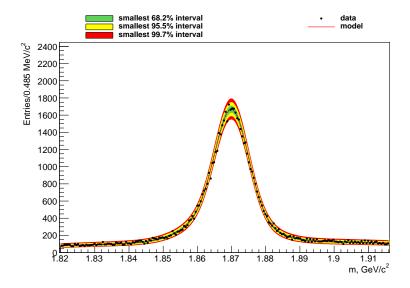

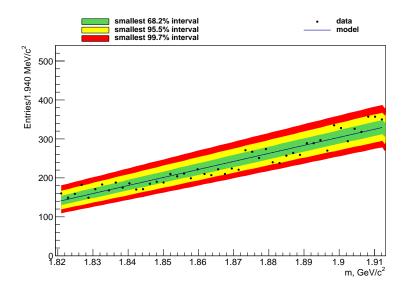

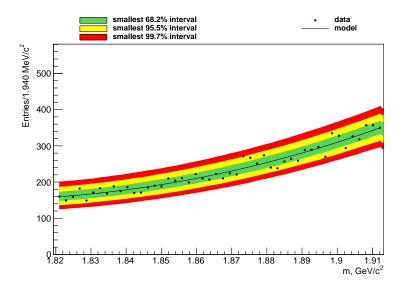

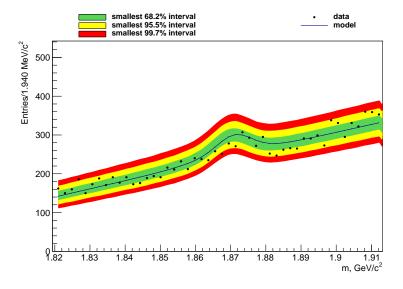

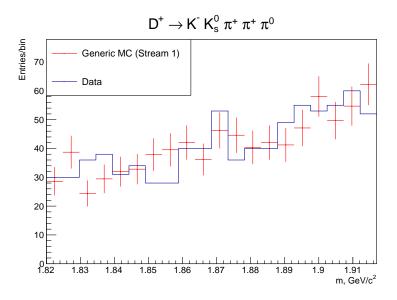

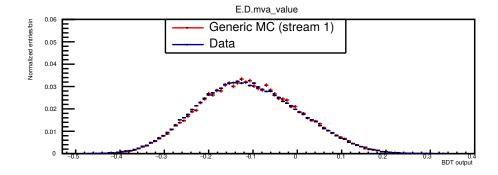

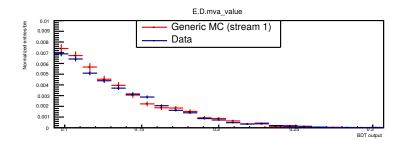

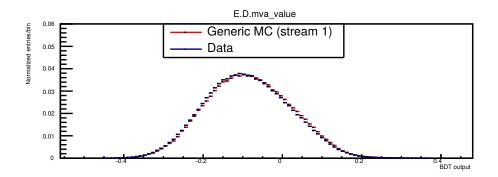

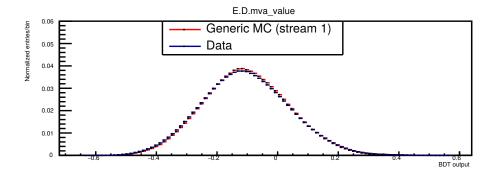

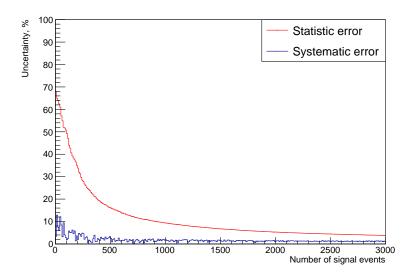

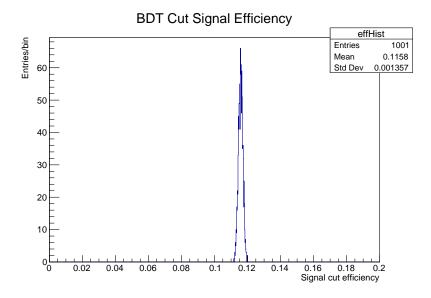

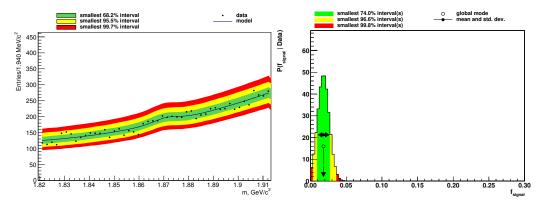

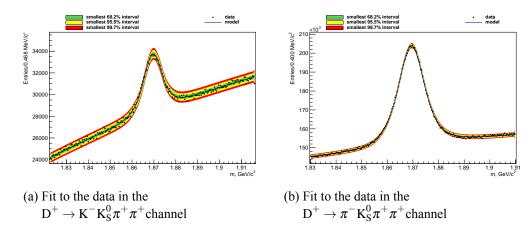

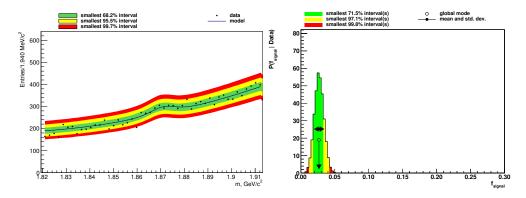

#### 5.4.1. Background Reduction with Boosted Decision Trees