## Università degli Studi di Napoli "Federico II"

Scuola Politecnica e delle Scienze di Base Area Didattica di Scienze Matematiche Fisiche e Naturali

Dipartimento di Fisica "Ettore Pancini"

Laurea Magistrale in Fisica

## FPGA-based Self-repairing Digital Circuits Design for the Belle II Experiment

**Relatore** Dott. Raffaele Giordano Candidato Sara Massarotti Matricola N94/394

A. A. 2019/2020

## Contents

| Contents                                                   |                                                             |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

|------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| trodu                                                      | uction                                                      |                                                                                                                                                                                                                                                                                                                                | vi                                                                                           |  |  |  |  |

| The Belle II experiment                                    |                                                             |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

| 1.1                                                        | Physic                                                      | es motivation and overview                                                                                                                                                                                                                                                                                                     | 1                                                                                            |  |  |  |  |

| 1.2                                                        | 1.2 SuperKEKB collider                                      |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

|                                                            | 1.2.1                                                       | Background at Belle II                                                                                                                                                                                                                                                                                                         | 7                                                                                            |  |  |  |  |

|                                                            | 1.2.2                                                       | Beam-induced background                                                                                                                                                                                                                                                                                                        | 7                                                                                            |  |  |  |  |

|                                                            | 1.2.3                                                       | Luminosity-dependent background                                                                                                                                                                                                                                                                                                | 8                                                                                            |  |  |  |  |

| 1.3                                                        | .3 The Belle II detector                                    |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

|                                                            | 1.3.1                                                       | Vertex detector (VXD) $\ldots$                                                                                                                                                                                                                                                                                                 | 10                                                                                           |  |  |  |  |

|                                                            | 1.3.2                                                       | Central Drift Chamber (CDC)                                                                                                                                                                                                                                                                                                    | 12                                                                                           |  |  |  |  |

|                                                            | 1.3.3                                                       | Particle Identification System (PID)                                                                                                                                                                                                                                                                                           | 13                                                                                           |  |  |  |  |

|                                                            | 1.3.4                                                       | Electromagnetic calorimeter (ECL)                                                                                                                                                                                                                                                                                              | 15                                                                                           |  |  |  |  |

|                                                            | 1.3.5                                                       | Superconducting coil                                                                                                                                                                                                                                                                                                           | 16                                                                                           |  |  |  |  |

|                                                            | 1.3.6                                                       | $K_L$ and $\mu$ system                                                                                                                                                                                                                                                                                                         | 17                                                                                           |  |  |  |  |

| 1.4                                                        | Monitoring radiation effects in detectors and electronics   |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

|                                                            | 1.4.1                                                       | The BEAST II: SuperKEKB Commissioning Detector                                                                                                                                                                                                                                                                                 | 18                                                                                           |  |  |  |  |

|                                                            | 1.4.2                                                       | System for Monitoring Radiation Effects in Field Programmable                                                                                                                                                                                                                                                                  |                                                                                              |  |  |  |  |

|                                                            |                                                             | Gate Arrays in BEAST II                                                                                                                                                                                                                                                                                                        | 20                                                                                           |  |  |  |  |

| Rad                                                        | liation                                                     | Damage in Electronic Components                                                                                                                                                                                                                                                                                                | 22                                                                                           |  |  |  |  |

| 2.1 Overview of radiation effects in electronic components |                                                             |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

| 2.2                                                        | 2.2 Total dose-based effects                                |                                                                                                                                                                                                                                                                                                                                |                                                                                              |  |  |  |  |

|                                                            | <b>The</b><br>1.1<br>1.2<br>1.3<br>1.4<br><b>Rad</b><br>2.1 | The       Belle         1.1       Physic         1.2       Superl         1.2.1       1.2.1         1.2.2       1.2.3         1.3       The B         1.3.1       1.3.2         1.3.3       1.3.4         1.3.5       1.3.6         1.4       Monitulation         1.4.1       1.4.2         Radiation         2.1       Overv | troduction         The Belle II experiment         1.1       Physics motivation and overview |  |  |  |  |

#### Contents

|                 |      | 2.2.1                                               | Displacement damage                                        |   | • |    |   | 24 |  |

|-----------------|------|-----------------------------------------------------|------------------------------------------------------------|---|---|----|---|----|--|

|                 |      | 2.2.2                                               | Total ionizing dose effects in devices                     |   | • |    |   | 30 |  |

|                 | 2.3  | Single event effects                                |                                                            |   |   |    |   | 35 |  |

|                 |      | 2.3.1                                               | Hard errors                                                |   | • |    |   | 37 |  |

|                 |      | 2.3.2                                               | Soft errors                                                |   | • |    |   | 38 |  |

| 3               | Sing | rle Eve                                             | ent Effects and Mitigation Techniques in FPGA              |   |   |    |   | 43 |  |

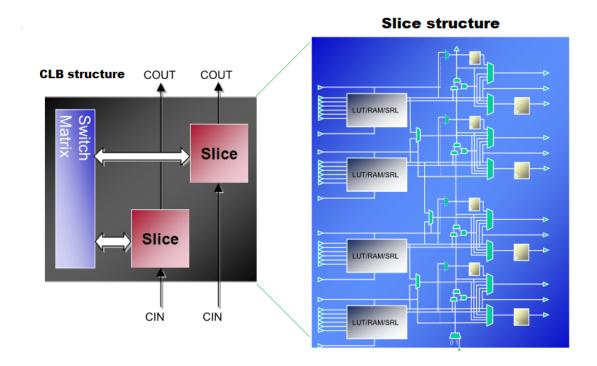

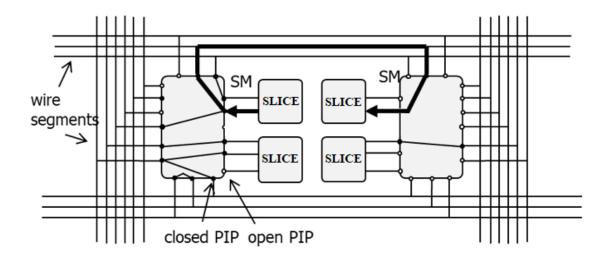

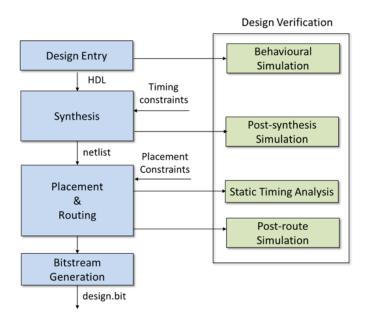

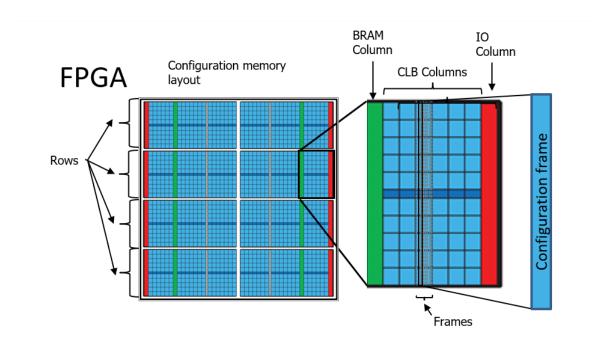

| 0               | 3.1  | Field Programmable Gate Arrays structure            |                                                            |   |   |    |   |    |  |

|                 | 3.2  |                                                     | rrors in SRAM FPGAs                                        |   |   |    |   |    |  |

|                 | 3.3  |                                                     | ation techniques                                           |   |   |    |   |    |  |

|                 | 0.0  | 3.3.1                                               |                                                            |   |   |    |   |    |  |

|                 |      | 3.3.2                                               | Triple Modular Redundancy                                  |   |   |    |   |    |  |

|                 |      | 3.3.3                                               | TMR-based configuration scrubbing                          |   |   |    |   |    |  |

|                 |      | 3.3.4                                               | SEM controller                                             |   |   |    |   |    |  |

|                 |      | 0.0.4                                               |                                                            | • | • | •• | • | 00 |  |

| 4               | The  | e Configuration Consistency Corrector in BEAST II 6 |                                                            |   |   |    |   |    |  |

|                 | 4.1  | FPGA                                                | a monitoring system at Belle II                            |   | • |    |   | 64 |  |

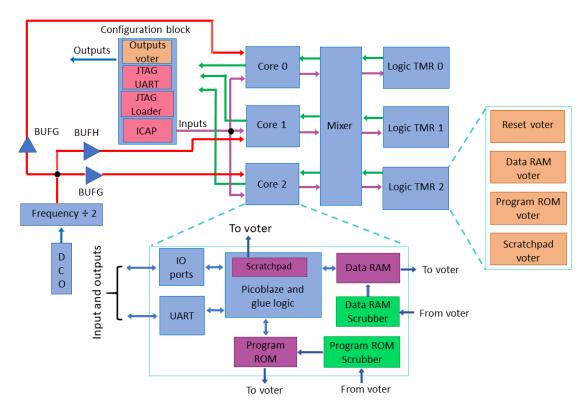

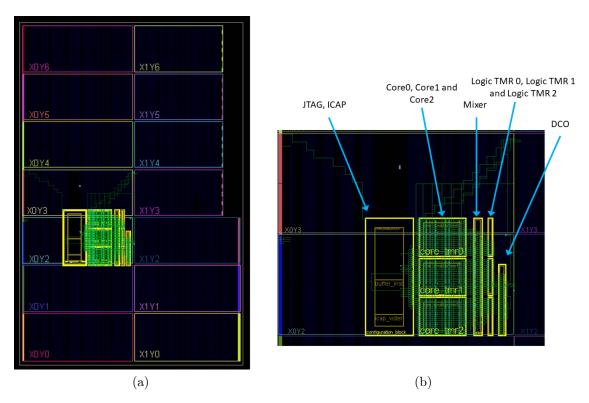

|                 | 4.2  | Redur                                               | ndant-configuration-based Scrubber architecture            | • | • |    |   | 67 |  |

|                 |      | 4.2.1                                               | The digitally-controlled oscillator                        |   | • |    |   | 69 |  |

|                 |      | 4.2.2                                               | JTAG Loader                                                |   | • |    |   | 75 |  |

|                 | 4.3  | Softwa                                              | are                                                        |   | • |    |   | 79 |  |

|                 | 4.4  | Plain $C^3$ implementation                          |                                                            |   |   | 84 |   |    |  |

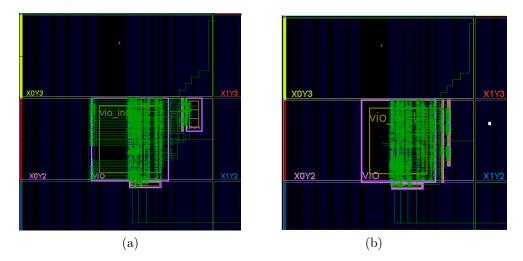

|                 | 4.5  | Isolati                                             | on design flow                                             |   | • |    |   | 87 |  |

|                 | 4.6  | IDF C                                               | $\mathbb{C}^3$ implementation                              | • | • |    |   | 90 |  |

| 5               | Fau  | lt inje                                             | ction Test Results                                         |   |   |    |   | 94 |  |

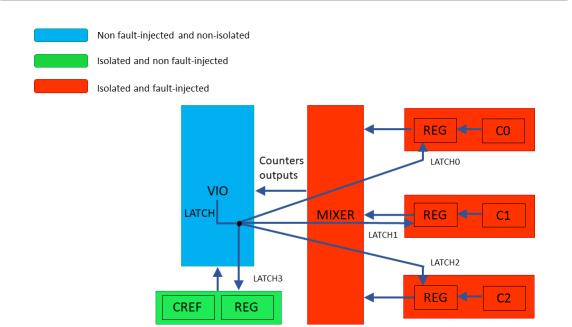

|                 | 5.1  |                                                     | ation of the Xilinx isolation design flow on test circuits |   |   |    |   | 94 |  |

|                 | 5.2  |                                                     | valuation test results                                     |   |   |    |   |    |  |

|                 | 5.3  |                                                     | ber software and hardware test setup                       |   |   |    |   |    |  |

|                 | 5.4  |                                                     | sts results                                                |   |   |    |   |    |  |

|                 | 5.5  |                                                     | ns learned                                                 |   |   |    |   |    |  |

|                 |      |                                                     |                                                            |   |   |    | - |    |  |

| Conclusions 116 |      |                                                     |                                                            |   |   |    |   |    |  |

Contents

### Bibliography

#### 118

## Introduction

High Energy Physics (HEP) detectors produce a huge amount of data per unit time (Tbps and more), thus requiring dedicated trigger and data acquisition (TDAQ) systems with real-time processing capabilities. Belle II is an HEP experiment at the rare/precision frontier, that requires very selective on-line triggering and real-time processing of the produced data. Indeed, it is designed for the measurements in the heavy flavour sector of the Standard Model (SM) and to search for New Physics (NP). Belle II is designed to study the B mesons and weak decays for the measurement of CP symmetry violation. The Belle II detector is built at SuperKEKB at the KEK laboratory in Tsukuba, Japan. It is an  $e^+ - e^-$  collider with an unprecedented design luminosity of  $8 \times 10^{35}$  cm<sup>-2</sup>s<sup>-1</sup>. Belle II comprises both detectors and electronics, operating for the off-detector readout operations and on-detector real-time processing and data transfer. The on-detector digital electronics based on programmable devices has been increasingly being used over the last two decades. In particular, static RAM-based Field Programmable Gate Arrays (SRAM-based FP-GAs) are increasingly used on-detector. They are reconfigurable, offer high-speed processing capability, embed dedicated resources for high-speed I/O and for Digital Signal Processing (DSP). Due to the SuperKEKB operation, detectors and electronics operate in a radiation environment, that may impact their functionality. The Beam Exorcism for a Stable Experiment II (BEAST II) commissioning detector has been designed to measure the radiation effects and to prevent radiation damage of detectors and electronics. It comprises a monitoring system for radiation effects on three SRAM FPGAs, selected due to their use in some Belle II sub-detectors.

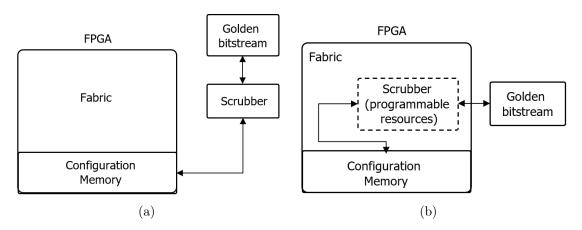

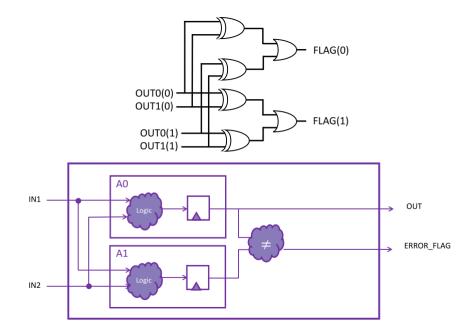

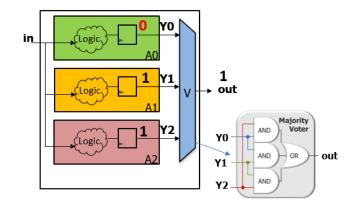

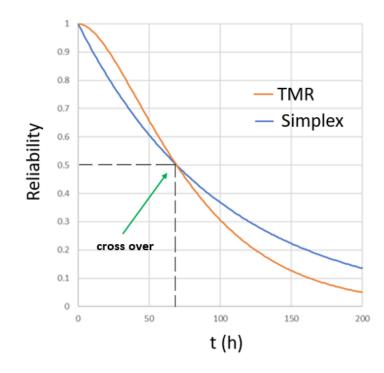

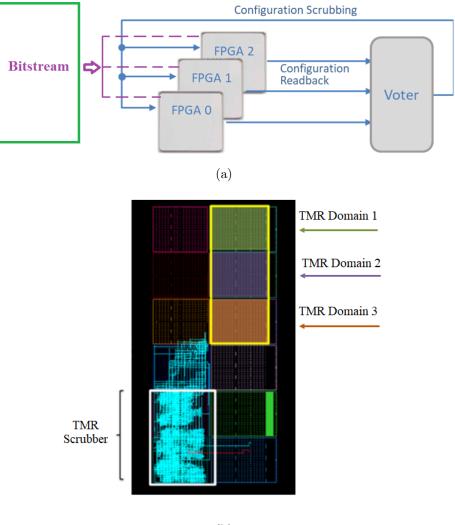

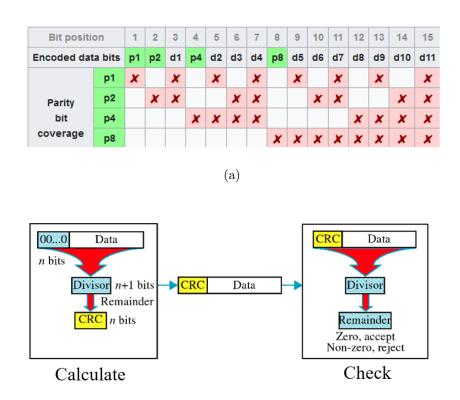

The main issue with the usage of FPGAs in radiation environments are single event upsets (SEUs) in the configuration memory. These SEUs might generate an unintended behaviour of the firmware. In order to preserve the correct functionality of the circuit, several mitigation techniques for radiation-induced errors have been developed. They can be split in two main categories: redundacy- and reconfiguration-based techniques. Such methods operate at different levels. Indeed, the first group acts to mask the error effects in the circuit, whereas the second directly manipulates the configuration, restoring the original configuration of the circuit. Since masking does not prevent SEU accumulation, redundancy-based methods are advantageous when combined to the reconfiguration-based ones. Among the redundancy-based techniques, the Triple Modular Redundancy (TMR) approach is the most used, consisting in majority voting the outputs of three copies of the same circuit. Instead, the reconfiguration method, also known as the configuration scrubbing, is performed by periodically correcting the FPGA configuration. This can be performed with a variety of techniques from a simple overwrite to the usage of redundant configuration or error correcting codes

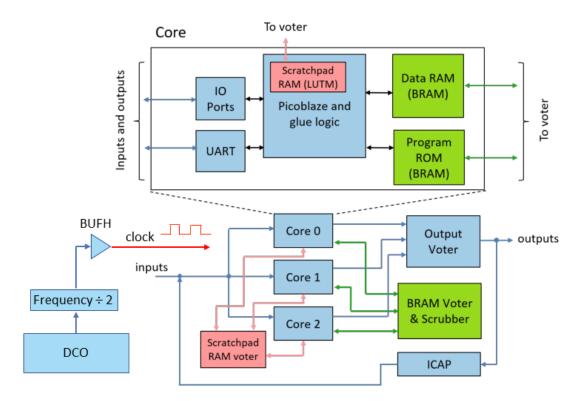

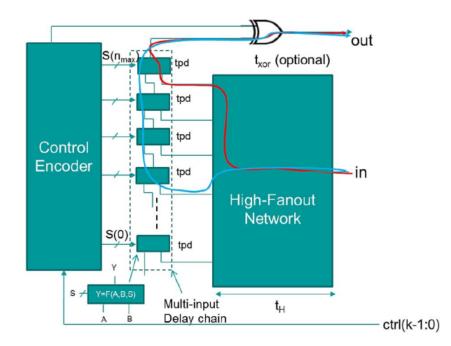

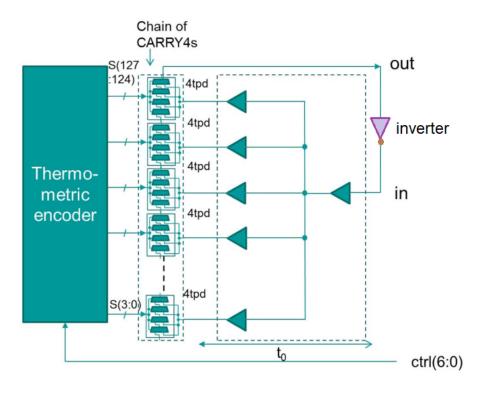

In this thesis work, I have designed and implemented a self-repairing circuit based on the redundancy of the configuration memory on a single Xilinx FPGA of BEAST II (XC7K325T). The proposed self-repairing system, named the Configuration Consistency Corrector  $(C^3)$ , leverages both TMR and configuration scrubbing. In particular, the redundancy of the configuration allows to implement a self-repairing circuit without external memories, i.e. the resources needed to protect the FPGA firmware are all included within it. Moreover, an internal digitally-controlled-oscillator (DCO) generates the system clock to the scrubber, providing a fully self-contained system. As a starting point, I have considered the architecture designed for another FPGA and I have adapted it to the BEAST II FPGA. Furthermore, I have enhanced its functionality by modifying the software organization, and I have further facilitated the software debugging which in turn simplified the tests on the circuit functionality. In particular, the changes on the software have been aimed to enhance the versatility of the circuit, in order to improve its portability onto other BEAST II FPGAs. As far as the software debugging is concerned, my work allowed to update the program executed by the device without regenerating the circuit firmware. I have also added a software check for the protection of circuit functionality and device. Finally, I have added commands for improving the fault-injection testing of the circuit. Since the system frequency is a key parameter, I have conceived a calibration system of the internal digitally controlled oscillator to determine its best value according to the oscillator layout.

I have studied a particular technique of design flow supported by Xilinx, the Isolation Design Flow (IDF). It is conceived to optimize the isolation between different modules within the same FPGA device and enhance the reliability without using multiple device. Thus, I have modified the previous architecture in order to implement a second version of the self-repairing circuit according to the IDF requirements.

Finally, I have designed and performed dedicated tests to evaluate the self-repairing capability of the two versions. These tests aimed to simulate SEU effects on the circuits. In particular, they are able to identify the bits defining the circuit functionality and drive the circuit itself to corrupt them and attempting self-repair. Then, I have identified the configuration memory bits causing a circuit failure, i.e. which cannot be self-corrected, and I have performed a statistical analysis on their distribution for the two proposed circuits.

The outline of the thesis is the following:

- in Chapter 1, I introduce the Belle II experiment with the BEAST II commissioning detector and its FPGA monitoring system;

- in Chapter 2, I describe the radiation effects on the electronic components;

- in Chapter 3, I focus on the mitigation techniques for SEUs effects in the configuration memory of the SRAM-based FPGAs;

- in Chapter 4, I present two self-repairing circuit implementations;

- in Chapter 5, I describe and analyse the fault-injection test results on tests circuits and on the implemented self-repair circuits.

## Chapter 1

## The Belle II experiment

#### 1.1 Physics motivation and overview

The Belle II experiment is an High-Energy Physics experiment at the rare/precision frontier designed for the measurements in the heavy flavour sector of the Standard Model (SM) and to search for New Physics (NP) phenomena. To reach these purposes, the Belle II experiment aims for an unprecedented target luminosity and is designed to study the B mesons weak decays. The latter have an important impact on models beyond the Standard Model (BSM). Indeed, if a charged Higgs existed [1], branching ratios in the decays  $B \to \tau \nu$  and  $B \to D^* \tau \nu$  could be modified, leading to deviations from SM predictions. The high luminosity at SuperKEKB, the collider for the Belle II experiment, allows to determine the branching ratios with unprecedented sensitivity. Furthermore, the measurement of CP symmetry violation in the B meson weak decays has been improved compared to the Belle experiment, and it is aimed to explain the matter-antimatter asymmetry in the NP scenario. CP symmetry violation observed in such processes is allowed in the SM if a nonzero phase appears in the standard parametrization of the Cabibbo-Kobayashi-Maskawa (CKM) matrix, V in the following. V successfully predict the CP violation adding a third generation of quarks, the bottom quark, to the starting non-CP-violated Cabibbo formulation of 1963. This formulation was pointed out by Kobayashi and Maskawa in 1973, that theorized the existence of the bottom quark as the only way to have a realistic model of CP violation. Indeed, such a particle was discovered in 1977 the bottom quark and its antiparticle are the main constituents of the B mesons. As a consequence, the CKM provides a flavour mixing of three quarks in weak decays, connecting the mass eigenstates (d, s, b) with the corresponding weak eigenstates (d', s', b'):

$$\begin{pmatrix} d'\\s'\\b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub}\\V_{cd} & V_{cs} & V_{cb}\\V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d\\s\\b \end{pmatrix}$$

(1.1)

The V matrix is a unitary matrix fully defined by four independent real parameters: three mixing angles  $\theta_{i,j}$  and the CP-violating phase  $\delta$  in the standard representation. Experimental data and the unitarity condition  $\mathbf{V}^{\dagger}\mathbf{V} = \mathbb{I}$  give an estimation of the three angles in addition to a specific hierarchy involving their sines. These conditions can be implicitly taken into account by considering the Wolfenstein parametrization [2]. The latter is derived from the observation that V differs from the unity I by a small quantity, due to the value of  $V_{us}$  equal to 0.22, the measurement of B mesons lifetime yielding to  $V_{cb} \simeq 0.06$ , and other experimental information. Thus, by replacing  $V_{us}$  by  $\lambda$ ,  $V_{cb}$  can be expressed as  $A\lambda^2$  with  $A \simeq 5/4$ . Finally, the unitarity condition allows to write V in the final form to order  $\lambda^3$

$$V \simeq \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\rho - i\eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3(1 - \rho - i\eta) & -A\lambda^2 & 1 \end{pmatrix} + \mathcal{O}(\lambda^4), \quad (1.2)$$

where  $\rho$  and  $\eta$  are new parameters, whose combination  $\rho - i\eta$  allows a direct calculation of the CP-violating phase. The Wolfenstein representation is an approximation of the standard representation and, unlike the latter, shows parameters of the same order of magnitude.

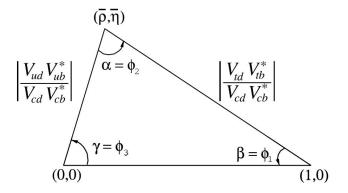

The unitarity of the CKM matrix implies the existence of relations between the rows and the columns of the matrix itself and these relations are represented as triangles in the complex plane. The most common used triangle is described by the relation  $V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0$  and is depicted in Fig. 1.1. The angles of such triangles can be calculated by measuring the CP symmetry violation, with the most relevant contribution coming from the observation of different B meson weak decay channels.

Figure 1.1: The Unitarity Triangle.

In the Belle II experiment, B mesons are produced in pairs  $B^0\overline{B}^0$  from the decay of  $\Upsilon(4S)$ , that is an accessible resonance with invariant mass  $m_{\Upsilon(4S)} \simeq 10.58 \ GeV/c^2$ in the electron-positron collision performed by the SuperKEKB asymmetric collider. Therefore, SuperKEKB allows to realize a second-generation B-Factory in the Belle II experiment as the new generation B-Factory. The  $\Upsilon(4S)$  resonance has a quark composition  $b\bar{b}$  and is the lightest resonance with a mass sufficient to decay in bflavoured mesons. The process  $e^+e^- \rightarrow \Upsilon(4S)$  is selected by choosing an energy of the  $e^+ - e^-$  system in the centre of mass frame equal to  $\simeq 10.58$  GeV, and this is convenient due to the branching ratio  $\mathcal{B}(\Upsilon(4S) \to B^0 \overline{B}^0) \simeq 48\%$  [3]. The B mesons pair is produced in an entangled quantum state in order to assign opposite and distinct flavours to  $B^0$  and  $\overline{B}^0$ . The  $\Upsilon(4S)$  resonance is produced boosted with respect to the laboratory frame (i.e., the detector rest frame) [4], due to the different energies of electron and positron beams. A suitable difference between the latter is needed to enhance the lifetime of B mesons and, therefore, to improve the detection of  $B^0$  and  $\overline{B}^0$  particles. Instead,  $B^0\overline{B}^0$  pair is produced almost at rest with respect to  $\Upsilon(4S)$   $(m_{\Upsilon(4S)} - 2mB^0 \simeq 19MeV)$ , so that in the laboratory frame B mesons have almost the same flight direction of the boost. The final Lorentz boost factor of the  $B^0\overline{B}^0$  pair centre of mass frame is  $\beta\gamma = 0.28$ , corresponding to a B meson mean flight distance of 130  $\mu m$ . This value is sufficient to track the vertices of the B mesons, but is reduced compared to KEKB ( $\beta \gamma = 0.42$ ). To obtain the same  $\beta \gamma$  of KEKB, the energy of the positron beam should be reduced (from 4 GeV to 3.5 GeV), but this implies higher beam losses not sustainable for the luminosity requirements.

In the next sections SuperKEKB collider and Belle II detector will be described,

as the main parts of the Belle II experiment.

#### 1.2 SuperKEKB collider

The SuperKEKB collider has been designed as the upgrade of the KEKB collider [5, 6], shut down in 2010, and is located at KEK (High-Energy Accelerator Research Organization) in Tsukuba, Japan. A key parameter improved in SuperKEKB compared to KEKB is the luminosity, measured as instantaneous and integrated luminosity. Given an event having a cross section  $\sigma$  and a number of events per unit of time dN/dt, the instantaneous luminosity is defined as

$$\mathcal{L} = \frac{1}{\sigma} \frac{dN}{dt}.$$

(1.3)

Instead, the integrated luminosity is  $\int \mathcal{L}dt$ . Whereas KEKB collider reached an instantaneous luminosity of  $2.11 \times 10^{34} cm^{-2} s^{-1}$ , SuperKEKB collider has a target full peak instantaneous luminosity of  $8 \times 10^{35} cm^{-2} s^{-1}$  - 40 times higher than KEKB one - reachable by 2022 and a target integrated luminosity of 50  $ab^{-1}$  by 2025. On 21th June 2020, SuperKEKB achieved the world's highest luminosity for a colliding-beam accelerator, setting a record of  $2.40 \times 10^{34} cm^{-2} s^{-1}$ .

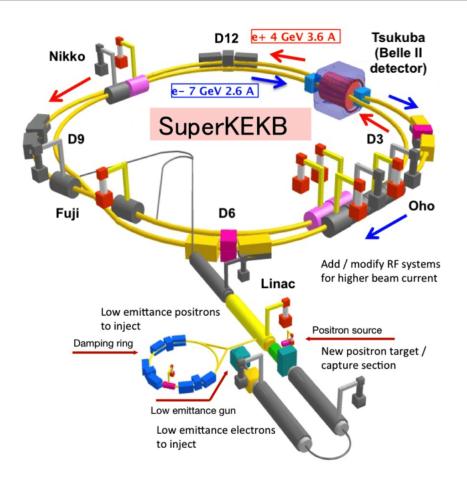

The SuperKEKB accelerator is shown in Fig. 1.2 and consists of a Low Energy Ring (LER) for the positron beam, a High Energy Ring (HER) for the electron beam, and an injector linear accelerator (Linac) 600 m long supported by a 1.1 GeV positron damping ring (DR). The electrons are produced in a pre-injector by a pulsed laser directed on a cold cathode target, giving a positron bunch with a charge of 4.4 nC and emittance<sup>1</sup> of 10 mm mrad, and then injected in the Linac. Here, the positron beam is produced and injected in the SuperKEKB along with the electron beam.

• Positron beam. A high-current 10 nC electron beam is generated and directed toward a tungsten target located in the middle of the Linac. The obtained 4 nC positrons are guided through the DR in order to reduce the emittance of the beam by radiation damping [7]. Then, they are extracted by

<sup>&</sup>lt;sup>1</sup>Formally, the beam emittance is defined as the phase space surface occupied by the beam. It is commonly used as a figure of merit to designate the quality of the beam spread.

Figure 1.2: Schematic drawing of the SuperKEKB accelerator. Linac preliminarly accelerates electrons and positrons, that then enter the HER (blue arrows) and the LER (red arrows).

a capture section and accelerated up to 4 GeV in the latter half of the Linac and injected in the LER.

• Electron beam. The electrons are accelerated to 7 GeV at the beginning of the Linac and injected in the HER.

Hence, Linac acts as two virtual independent accelerators for the electron and positron beams, changing parameters in a pulse-by-pulse basis at 50 Hz. Particles in the beams are grouped into bunches. Each ring can store 2506 bunches with roughly  $10^{11}$  particles per bunch. Newly accelerated bunches are continuously injected from the linear accelerator into the main storage rings. When new particles

enter the storage ring, it takes a few milliseconds until their emittance is sufficiently reduced.

The particle beams are brought to a collision at the interaction point (IP), which is surrounded by the Belle II detector. The area around the IP extends for about 4 m along the storage rings and is called interaction region (IR). It is equipped with quadrupole magnets for the final focusing of the beams. The beampipe around the IR consists of two Beryllium layers with Paraffin in-between them acting as a coolant. The high stiffness, low atomic number, good thermal stability as well as its diamagnetic nature validate the choice of Beryllium as beampipe material. The low atomic number is advantageous to suppress multiple scattering of particles coming from the IP and the diamagnetic properties ensure that no interference with the magnetic field of the focusing magnets can occur. An additional gold coating at the inside of the beampipe is used to suppress synchrotron radiation.

The LER and HER rings are divided into four arc sections (D3, D6, D9 and D12), hosting normal conducting dipole bending magnets to guide the particles around the ring, and four straight sections (Tsukuba, Oho, Fuji and Nikko). Both bent and straight sections are supported by focusing magnets and collimators in order to maintain a small diameter of the beam. Superconducting and normal conducting radiofrequency (RF) cavities are installed along the straight sections to mitigate the energy loss due to the synchrotron radiation. The latter is induced by the bending and focusing magnets along the storage ring that accelerate the beam particles, being present especially in the HER and giving emitted photons from few keV to tens of keV.

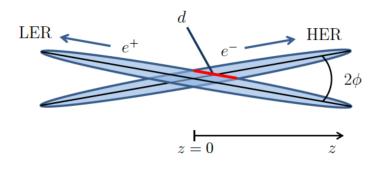

The method allowing to achieve the high target luminosity of SuperKEKB is the nano-beams scheme, developed by the Italian physicist Pantaleo Raimondi and used for the first time in this collider. The basic idea is to squeeze the electron and positron bunch beam sizes at the IP, in both the horizontal and vertical directions of the transversal plane, in order to increase the luminosity. Indeed, the latter varies inversely with cross-sectional area of the colliding beams. The luminosity is also proportional to the product of the two beam currents ( $\mathbf{L} \propto i_{e^+}i_{e^-}$ ), i.e., the numbers of particles colliding per unit of time. The crossing area is further reduced by increasing the crossing angle  $2\phi$  of the beams up to 83 mrad (Fig. 1.3), about four times compared to the KEKB one. The crossing angle is used to avoid a head-on

Figure 1.3: Geometry of the crossing angle.

collision, which would introduce various difficulties and disadvantages due to beam optical effects. Due to the beams squeezing at the IP and the increased crossing angle, the perturbation from the nominal trajectory of each beam is reduced by a factor 20 with respect to the KEKB case and the target luminosity can be obtained just by doubling the beams currents values of KEKB (1.64 A/1.19 A in KEKB and 3.60 A/2.62 A in SuperKEKB for electron and positron beams, respectively).

#### 1.2.1 Background at Belle II

The electron-positron collisions at the Belle II IP induce different undesired background processes. The interactions of the beam particles with each other or with residual gas in the beampipe constitute the beam-induced background, whereas the high beam current values in SuperKEKB provoke the luminosity-dependent background. The main sources of these two kinds of background are briefly described below.

#### 1.2.2 Beam-induced background

The first source of the beam-induced background is the Touschek effect [8], that is an intra-bunch Coulomb repulsive scattering. It occurs due to the high density of particles in a beam bunch needed for the high luminosity demand of SuperKEKB. Indeed, the larger the density of particles in a beam bunch, the higher the collision rate between particles within a bunch. Touschek effect is observed when the particle collisions have an energy so high that a particle leaves the bunch. Particles trajectories deviations also occur because of the interactions between the beam particles and the residual gas,  $H_2$  and  $CO_2$ , contained in the beampipe, that constitute the second source of the beam-induced background. However, the particles deviating from their nominal trajectories can collide with the beam-pipe inner wall, producing a shower. If the shower develops close to the interaction region, the shower particles can enter the sensitive part of the detector. Countermeasures used for Touschek background are efficient also for beam-gas background.

The last beam-induced background source is the synchrotron radiation, since, especially in the HER, particles have an energy loss in terms of emitted photons from few keV to tens of keV, as anticipated.

#### 1.2.3 Luminosity-dependent background

The luminosity-dependent background scales with the luminosity of the accelerator [9]. The background at SuperKEKB is therefore approximately 40 times larger compared to KEKB [10]. The high beam currents in SuperKEKB enhance the probability that the radiative Bhabha scattering  $e^+e^- \rightarrow e^+e^-\gamma$  occurs, having an a priori high cross section in electron-positron collisions. The scattered particles could lead to back-scattering into the detector, whereas the emitted photons could induce the emission of neutrons<sup>2</sup>, which are able to create severe damage in the sensors and electronics of the innermost part of the Belle II detector. Another important luminosity-dependent background sources are the low momentum  $e^+ - e^-$  pairs produced in the two-photon process  $e^+e^- \rightarrow e^+e^-\gamma\gamma \rightarrow e^+e^-e^+e^-$ , since they might spiral inside the detector.

#### 1.3 The Belle II detector

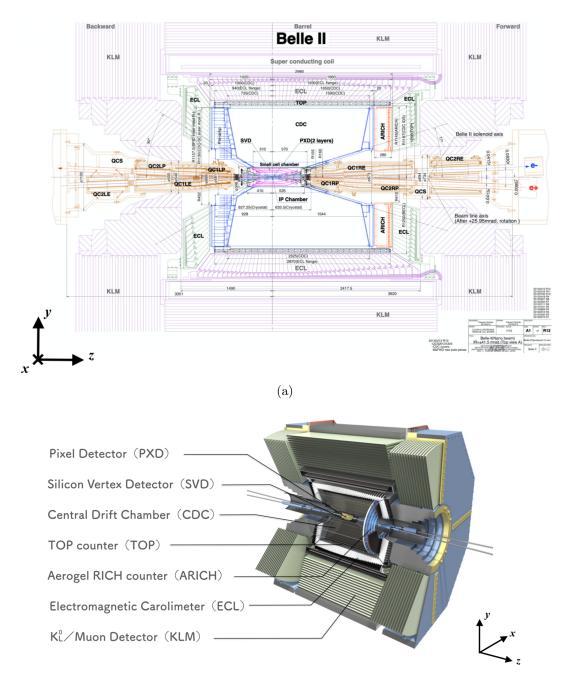

The Belle II detector is the upgrade of the Belle detector and it is installed at the SuperKEKB collider IP. In Fig. 1.4 a top view and a three-dimensional view of the detector are shown. It is designed to cope with higher backgrounds related to the higher luminosities. Also, it has been optimized for the  $B^0\overline{B}^0$  identification

$<sup>^{2}</sup>$ The photons produced in the electromagnetic showers hit pipe nuclei and extract neutrons.

(b)

Figure 1.4: The Belle II detector. (a) Detailed top view with all the sub-detectors , (b) three-dimensional sketch.

and reconstruction. Finally, the Belle II detector exhibits excellent vertexing and tracking capabilities allowing the discrimination of  $B^0$  from the  $\overline{B}^0$ .

The Belle II detector is conventionally described by a right-handed Cartesian coordinate system with the origin located at the nominal IP. The z-axis is parallel to the beampipe. The positive direction of the z-axis points to the forward region of the detector. The positive part of the y-axis points to the top of the detector and the orientation of the x-axis is parallel to the radial direction towards the outside of the detector ring. It has an asymmetric design to account for the forward boost in the direction of the electron beam. The angular acceptance of Belle II is in the range  $[17^{\circ}, 150^{\circ}]$  for the polar angle  $\theta$ , and it is  $2\pi$  for the azimuthal angle  $\varphi$ . With regard to the polar angle, the detector is divided into three regions:

- the forward region  $(17^{\circ} < \theta < 30^{\circ});$

- the barrel region  $(30^{\circ} < \theta < 125^{\circ});$

- the backward region  $(125^{\circ} < \theta < 150^{\circ})$ .

The regions differ in terms of detector set-up and material budget. The Belle II detector is composed of several sub-detector systems, for vertex finding, tracking and identifying the decay products. The sub-detectors are described in detail below.

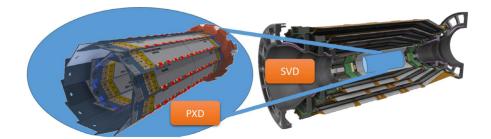

#### 1.3.1 Vertex detector (VXD)

The vertex detector in the Belle II experiment reconstructs the B-meson decay vertices with a precision of 100  $\mu m$ . The excellent position resolution improves the impact parameters when compared to Belle. It is a six-layer system forming a cylinder around the beampipe and consisting of two sub-detectors: the inner two-layer Pixel detector (PXD), mounted directly onto the beam pipe around the IP, and the outer four-layer Silicon vertex detector (SVD). The scheme of the detector is depicted in Fig. 1.5. The quality of the vertex reconstruction given by the VXD is related to different sensors constituting PXD and SVD. Due to the nano-beam scheme of SuperKEKB collider, the beampipe radius is just 10 mm allowing a good vertex reconstruction. As a consequence, the silicon vertex strip detectors, used in Belle, are no longer suitable for the innermost layers of the vertex detector because

Figure 1.5: Belle II Vertex Detector concept. In the picture, a magnified PXD (in the left) is surrounded by the SVD (in the right). [11]

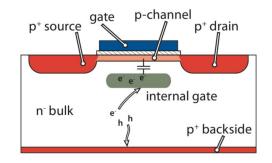

Figure 1.6: Schematic depiction of a p-channel DEPFET.

strip sensors have a large occupancy, defined as the fraction of channels hit in each triggered event. For this reason, the first two layers of VXD are composed of pixel sensors, that count a larger number of channels and therefore provide a smaller occupancy to improve the spatial resolution.

#### 1.3.1.1 Pixel detector (PXD)

The pixel sensors are distributed on two layers, at 14 mm and 22 mm from the IP, and are based on the DEPFET technology (DEPleted Field Effect Transistor) [12]. The latter allows to have granular, fast, lightweight, and very thin pixel sensors (50  $\mu$ m), that are also able to withstand the high-radiation environment. The DEPFET pixels consist in a p-channel MOSFET integrated onto a fully depleted n-type silicon bulk, with a  $p^+$  backside contact (Fig. 1.6). The bulk depletion generates a potential minimum, directly underneath the transition channel at a depth of about 1  $\mu$ m. Incident particles generate electron-hole pairs within the fully depleted bulk. While the holes drift to the back contact, electrons are accumulated in the potential minimum, called the internal gate. When the transistor is switched on, the electrons modulate the channel current. This scheme shows various intrinsic advantages:

- reduction of white and electronic noise <sup>3</sup>, even at room temperature, related to the small capacitance of the internal gate;

- signal amplification and direct readout, avoiding charge loss between collection and amplification;

- non-destructive readings of the stored charge, allowing for different readout schemes.

However, the charged particle tracking limits the PXD (and SVD) features mainly due to the multiple scattering. Indeed, the material budget is  $0.2\% X_0$  per layer.

#### 1.3.1.2 Silicon vertex detector (SVD)

The SVD detector is composed of four layers Double-sided Silicon Strip Detectors (DSSDs), placed at 38 mm, 80 mm, 115 mm, and 140 mm from IP. The average radii range between 3.8 cm (layer 3) and 13.5 cm (layer 6), covers 90% of the solid angle. The SVD detector employs several kinds of sensors differing by shapes and strip pitch. Furthermore, it is designed to optimize the resolution of the impact parameter and to sustain the background condition expected at full luminosity. As for the PXD, the material budget is limited, having a value of 1-2%  $X_0$  per layer in this case. In addition, due to the increase of a factor 40 in luminosity, the background-hit rate will be sensibly higher than the Belle B-Factory. Finally, the occupancy is kept under control by shorter strips.

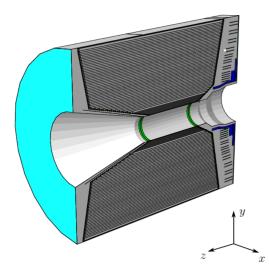

#### 1.3.2 Central Drift Chamber (CDC)

The CDC is a large volume  $\text{He-C}_2\text{H}_6$  50-50 drift chamber with three important purposes: trajectories measurement, momenta measurement, and energy loss of charged

<sup>&</sup>lt;sup>3</sup>Here, the electronic noise is referred to the 1/f or pink noise, where f indicates the signal frequency.

Figure 1.7: Schematic three-dimensional drawing of the CDC structure.

particles within its gas volume, for charged particles with momenta ranged from 50 MeV/c to 8 GeV/c. It contains 14336 wires arranged in 56 axial (parallel to the beampipe) or stereo (slanted with respect to the axial wires) layers, having the schematic structure reported in Fig. 1.7. Compared to the Belle CDC, Belle II CDC counts six more layers and almost a double number of sense wires, justified from the larger radii of the inner and outer cylinders and wires. Low-momentum tracks, which do not reach the subsequent particle identification system, can be identified using the CDC alone. Finally, the central drift chamber, gives reliable and efficient trigger signals for charged particles.

#### 1.3.3 Particle Identification System (PID)

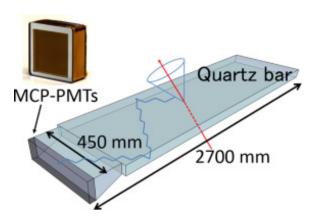

The particle identification (PID) system in the Belle II detector is needed to distinguish of charged particles such as pions, kaons, protons, electrons, and muons deriving from the  $B^0$  decays. This identification is performed by the ring-imaging Čerenkov detectors located in the barrel region and in the forward end-cap region, namely the Time of Propagation Counter (TOP) and the Aerogel Ring-Imaging Čerenkov counter (ARICH), respectively. Čerenkov detectors measure the  $\theta_c$  angle of photons emitted by relativistic charged particles crossing a radiator material, ob-

Figure 1.8: Single module of the TOP counter. The charged particles cross the quartz radiator bar and the emitted photons reach the MCP-PMTs by total reflections, also supported by the focusing mirror at the forward end of the bar.

taining  $\beta$  of the particle with the following relation  $\cos \theta_c = (\beta n)^{-14}$ , where n is the refractive index of material.

#### 1.3.3.1 TOP

The TOP counter is composed by 16 identical modules, that are arranged around the IP in a barrel-like geometry. As shown in Fig. 1.8, each module is composed of a quartz radiator bar, a focusing mirror at the forward end of the bar, and an array of micro-channel plate photomultipliers tubes (MCP-PMTs) at the backward end of the bar. Due to the high average refractive index of the quartz, the Čerenkov radiation produced by the radiator remains trapped by total reflection, propagating to the MCP-PMT array. Thanks to the pixel size of  $\simeq 5.5 \times 5.5 \text{ mm}^2$  and a transit time spread less than 50 ps, the MCP-PMTs provide a very precise measurement of position and detection time. Once the direction of the incoming particle is known, the time of propagation of the Čerenkov photons inside the quartz is only function of the Čerenkov angle. Therefore, the TOP provides a combined measurement of both time of flight  $t_{TOP}$  and Čerenkov angle. Overall, the TOP counter has a single photon time resolution of about 100 ps.

<sup>&</sup>lt;sup>4</sup>This relation derives from the distance covered by the Čerenkov radiation  $ct/n = \beta ct \cos \theta_c$ , where  $\beta c$  is the charged particle velocity in the material and c/n is the radiation velocity emitted at  $\theta_c$  with respect to the particle direction.

#### 1.3.3.2 ARICH

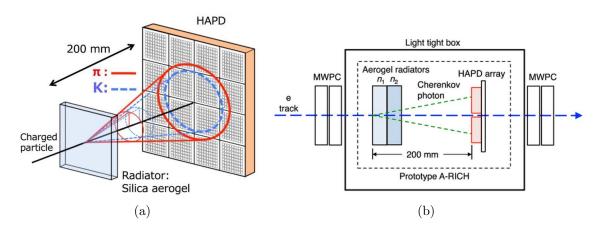

A fundamental requirement of the Belle II experiment is the identification of the charged particles over the full kinematic range of the experiment, ranging from a few tens of MeV/c to  $\approx 8$  GeV/c. In the forward end-cap, the subdetector achieves this goal. It is a proximity focusing Ring-Imaging detector schematized in Fig. 1.9 and having the structure described below.

- Aerogel tiles work as radiator to produce Cerenkov photons starting from incident charged particles.

- An expansion volume of 20 cm allows the Cerenkov photons to enlarge into rings on the surface of an hybrid avalanche photon detector (HAPD).

- The HAPD detects single photons, having the Cerenkov angle  $\theta_c$ .

- A read-out system collects electrical signals from the HAPDS.

The key parameter in the performance of a RICH counter is the Čerenkov angle resolution per track  $\sigma_{track} = \sigma_{\theta_c}/\sqrt{N_{\gamma}}$ , where  $\sigma_{\theta_c}$  is the single photon Čerenkov angle resolution and  $N_{\gamma}$  is the detected photons number. With a longer radiator,  $N_{\gamma}$ increases but  $\sigma_{\theta_c}$  degrades because of the emission point uncertainty. The peculiar solution for Belle II ARICH is using two layers of aerogel with different refractive indices ( $n_1 = 1.045$ ,  $n_2 = 1.055$ ) as a radiator of 2 cm thickness, so that the  $N_{\gamma}$ value is equivalent to a double radiator thickness and  $\sigma_{\theta_c}$  reaches an optimized value of  $\simeq 13$  mrad for charged tracks with momentum larger than 3.5 GeV/c, even if no significant degradations are shown for lower momentum tracks. Therefore, with  $N_{\gamma} \simeq 10$  per tile, the Čerenkov angle resolution per track is  $\sigma_{track} \simeq 3$  mrad. The angular acceptance is  $\theta \in [14^{\circ}, 30^{\circ}]$ .

#### 1.3.4 Electromagnetic calorimeter (ECL)

The employment of a high resolution electromagnetic calorimeter (ECL) in B-decays detector is of utmost importance because one third of the decay products are  $\pi^0$ 's or other neutral particles like  $K^0$ 's that provide photons in a wide enery range from 20 MeV to 4 GeV. The Belle II ECL uses the same scintillation crystal material, namely

Figure 1.9: The ARICH counter. (a) The principle of  $\pi$  and K identification. (b) The complete scheme for the Belle II ARICH by using two layers of aerogel with different refractive indices.

CSI(Tl) (thallium-doped cesium iodide), but is supported by a total upgrade of the read-out electronics to cope with the SuperKEKB increased luminosity. In addition to the photons energy and angle measurement, it contributes to the  $K^0$  detection with  $K_L$  and  $\mu$  system (KLM) detector.

The ECL comprises a barrel region, a forward end-cap, and a backward end-cap region, covering 90% of the solid angle in the centre of mass frame with an angular acceptance of  $\theta \in [12.01^{\circ}, 155.03^{\circ}]$ .

#### 1.3.5 Superconducting coil

The superconducting coil produces an homogeneous magnetic field  $\vec{B}$  of 1.5 T, parallel to the beam direction. The coil is made of NbTi/Cu, carrying a current of 4400 A and operating under a liquid helium cryogenic system. It encloses an internal cylindrical volume of radius r = 1.7 m and length of 4.4 m. The iron structure of the KLM works as the return yoke of the magnetic field to confine the latter. Therefore, in the region of the KLM outside the coil, the direction of  $\vec{B}$  is inverted.

#### **1.3.6** $K_L$ and $\mu$ system

The KLM task is to identify the muon tracks by measuring their penetration depth and to reconstruct the  $K_L^0$  by considering the combined information of ECL and the hadronic KLM showers. It is formed by alternating 4.7 cm iron plates and scintillators with silicon photomultiplier (SiPM) detectors surrounding the coil. As anticipated, the iron plates provide the magnetic flux return for the coil. Furthermore, they provide 3.9 interaction lengths ( $\lambda_0$ ) in addition to the  $0.8\lambda_0$  of the ECL, in which  $K_L^0$  can shower hadronically. Octagonal barrel covers the polar angle range from 45° to 125°, whereas backward and forward end-caps extend this coverage from 20° to 155°. The barrel has 15 detector layers and 14 iron plates, whereas each endcap has 14 detector layers and 14 iron plates. The barrel layers are Resistive Plate Chambers (RPCs):

- thoroughgoing charged particle ionizes the gas molecules along its path in a proportional gas chamber;

- an electric field accelerates the electrons toward the anode and the ions toward the cathode;

- a strong electric field enables a streamer mode, i.e., a significant enhancement of ionizations between the electrodes;

- dielectric foam surrounds the electrodes to prevent the propagation of sparks;

- the signal is read by means of metallic strips on one side of the chamber.

Compared to Belle detector, in the end-caps and the innermost layers in the barrel region the RPCs have been replaced by layers of scintillator strips with a read out by silicon photomultipliers (SiPMs). This upgrade is due to the long dead time of the RPCs, that significantly reduces the detection efficiency for the high background hit rates present in the Belle II detector. Moreover, this would give a large muon misidentification probability. On the contrary, the layers of scintillator strips have an high rates tolerance, although the large neutron background degrades the SiPMs and, therefore, considerably increases their dark count rate. Nevertheless, such a detector system can be reliably operated by appropriately shifting the discrimination threshold. The muons are identified starting from CDC tracks: each track is extrapolated to KLM region with a  $\pi$  mass hypothesis, and a KLM hit is assigned to that track if is present near the extrapolation region. A  $K_L^0$  can be reconstructed clustering all of the KLM hits within a 5° opening angle con from the IP, and then applying a charged track veto by means of a CDC track matching. If the remaining neutral KLM clusters are aligned within a cone of 15° with an ECL cluster, the two showers are associated. The  $K_L^0$  detection efficiency rises linearly from 0 at 0 GeV/c to a 80% plateau at 3 GeV/c. The angular resolution is about 3° for KLM-only candidates and 1.5° for KLM+ECL candidates. The SiPMs offer an excellent time resolution of  $\sigma_t \simeq 0.7$  ns, allowing to also measure the  $K_L^0$  time of flight.

### 1.4 Monitoring radiation effects in detectors and electronics

Once the sub-detectors structure in the Belle II detector has been described, the practical implementation issues related to the radiation effects must be discussed. Usually, detectors and electronics employed in the High-Energy Physics (HEP) experiments work in radiation environments, exposing the system to possible damage. The BEAST II (Beam Exorcism for a Stable Experiment II) is a commissioning detector designed to measure these effects, making it possible to prevent radiation damage on the sub-detectors and tuning models for background simulation. In the next subsections, the BEAST II structure and the monitoring system of specific electronic components, namely Field Programmable Gate Arrays (FPGAs), will be described. The concepts related to the radiation damage and their mitigation in the electronic integrated circuits, will be more deeply treated in the next chapters.

#### 1.4.1 The BEAST II: SuperKEKB Commissioning Detector

The BEAST II is a SuperKEKB commissioning detector, needed to prevent radiation damage to the Belle II detector and to improve simulations of beam-induced backgrounds near the IP. Indeed, the experience with KEKB has shown that the measurement of the particle and X-ray backgrounds around the IP is crucial to ensure the radiation to be sufficiently low before the vertex detector is installed. During the Phase 1 of the Belle II data taking<sup>5</sup>, BEAST II consisted of eight detector systems described below [13].

- In 32 points near the IP, there are 64 PIN diodes, not biased to simplify the associated electronics, which provide the monitoring of the ionization radiation dose. Ionizing radiation leaves a free electrons and holes trail with a consequent enhancement of the dark current from the PIN diodes. The integral of this amplified current is proportional to the ionizing radiation dose.

- A system made of single-crystal diamond detectors performs the monitoring of the instantaneous and integrated radiation doses. This system is designed to preserve the vertex detector, due to the their exposition to the largest radiation doses. The readout electronics system offers continuous monitoring of radiation doses and also aborts the signals related to beam losses corresponding to an excessive levels of luminosity.

- An inorganic scintillator electromagnetic calorimeter, namely "Crystals", measures the electromagnetic background radiation in the innermost part of Belle II ECL. As in the latter, similar position and detection technology is employed to simulate the observed measurements. Indeed, Crystals has an accurate time resolution for bunch-by-bunch beam-induced backgrounds and for the injected backgrounds relative to the Touschek and beam-gas contributes. The Crystals system is composed of six identical units, each containing three crystals read-out by means PMTs. The three crystal types are CsI(Tl), pure caesium iodide, CsI(pure), and cerium-doped lutetium yttrium orthosilicate, LYSO. The CsI and LYSO crystals operate in a fast read-out mode to measure the time structure of injection backgrounds.

- A detector system consisting in a bismuth germanium oxide (BGO) monitors the real-time beam backgrounds as electrons and gammas. Furthermore, the BGO monitors the luminosity of the collider as well, by counting Bhabha

<sup>&</sup>lt;sup>5</sup>Phase 1 consisted in the SuperKEKB commissioning to characterize the beam environment and from Feb. to June 2016.

events rate for focused beam. In the Belle II experiment, eight BGO crystals sensors are installed around the IP: four in the forward region and four in the backward region, with light-tight treatments applied to the BGO in order to ensure maximum light-collection efficiency and to prevent leakage of environmental light.

- A system composed by eight plastic scintillators tiles read-out with SiPMs, namely CLAWS, measures background levels connected to injection with time resolution higher than the bunch crossing frequency (250 MHz). The CLAWS measures the total rate and the exact time arrival of minimum-ionizing particles (MIPs). Finally, the CLAWS are sensitive to MeV neutrons.

- <sup>3</sup>He detector system consisting of <sup>3</sup>He tube system measures the rate of thermal neutrons (kinetic energy of ~ 0.25eV). Each detector is a stainless steel cylinder with 5.08 cm in diameter and 20.38 cm in length, filled with <sup>3</sup>He and a small amount of CO<sub>2</sub> at a pressure of 4 atm. In the centre of the tube there is a sense wire, which is set to a voltage of 1.58 kV. The <sup>3</sup>He tubes are located above, below, and on either side of the IP.

- A system of four Time Projection Chambers (TPC) provides the direction and the energy measurements of fast neutron recoils produced by the various beam backgrounds. The TPCs are located around the IP at φ = 0°, 90°, 180°, and 270°. The TPCs provide detailed 3D measurements of charge density distributions via micro pattern gas detectors.

#### 1.4.2 System for Monitoring Radiation Effects in Field Programmable Gate Arrays in BEAST II

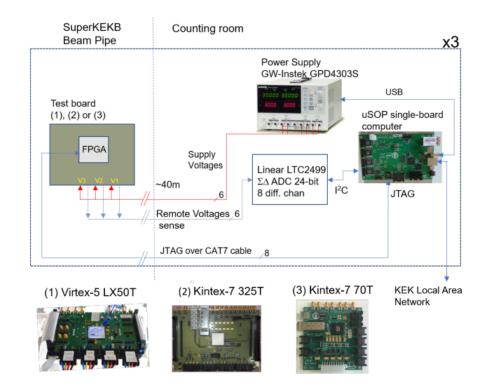

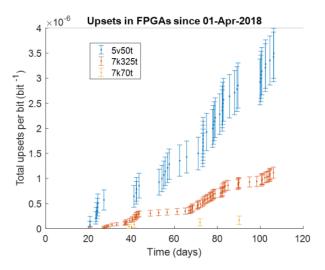

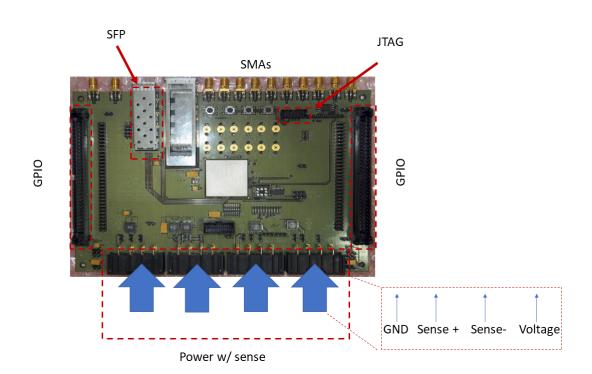

As anticipated, the main purpose of BEAST II is monitoring the effects of the radiation environment surroundings the detector. The radiation impact is linked to both detector systems, for the vertex sub-detector protection, and the electronic components. Among the latter, the static RAM-based FPGAs (SRAM-based FP-GAs) are widely used in trigger and data acquisition system of Belle II detector, due to their re-configurability and large data processing and transfer capabilities. For this reason, three test boards hosting Xilinx FPGAs are included in BEAST II. Two boards host Kintex-7 (70T and 325T), one hosts Virtex-5 LX50T FPGAs. The specific FPGA families have been chosen basing on their use in two Belle II sub-detectors:

- Virtex-5, since it is installed the CDC for read-out data;

- 7-series, since it is installed on the TOP counter

Virtex-5 LX50T and Kintex-7 325T are installed on the forward side of the detector at about 10 m from the IP along z-axis, whereas Kintex-7 70T is installed on the backward side of the IP at about 7 m. The different installation positions are needed to investigate the inhomogeneous radiation environments created by the asymmetric colliding. In the radiation tolerance field, Single Event Effects (SEE), mainly Single Event Upsets (SEUs) in the configuration memory, affect and damage the FPGAs. Although the scaling of technological processing allows high total dose hardness levels in the FPGAs, the development of SEU impact mitigation techniques are needed and they will be deeply examined in the Chapter 3 whereas the radiation damage in the electronic component will be discussed in the next Chapter.

## Chapter 2

## Radiation Damage in Electronic Components

In HEP, silicon-based technology is widely used for detectors and readout systems. In this chapter the radiation effects on the electronic components will be discussed, referring to silicon unless differently indicated.

# 2.1 Overview of radiation effects in electronic components

The matter-radiation interaction has a key role in the functionality of electronic devices. Indeed, it could induce damage essentially as alteration of the crystal structures or undesired production of charge carriers, giving macroscopic effects in the circuits behaviour. Therefore, the radiation effects can be split in two categories based on the radiation-damage mechanism and described below.

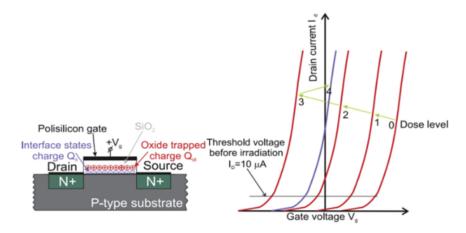

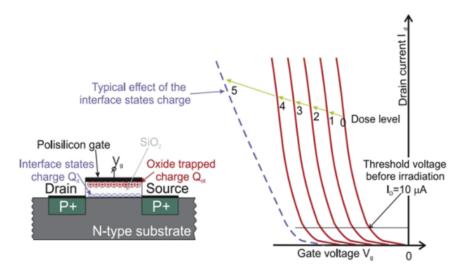

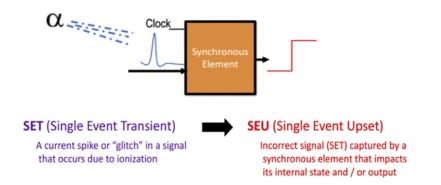

• Ionization damage. The ionization effect can occur as cumulative effect related to the concept of total ionizing dose (TID) - or as single event effect (SEE). The cumulative effect occurs when the energy absorbed in a semiconductor or insulating layer produces free charge carriers, i.e., electron-hole pairs. The latter diffuse or drift to other locations, being trapped in some cases. However, the consequent charge accumulation leads to a parasitic field. This effect is the primary one in X-rays,  $\gamma$ -rays exposition, and charged particles, and it is important in devices based on surface conduction as the metal-oxide-silicon field effect transistors (MOSFETs). SEEs are related to the charge deposition induced by a single particle crossing a sensitive region of the device.

• **Displacement damage**. Incident radiation displaces atoms from their lattice sites, altering the structure and the electrical characteristics of the crystal. Therefore, displacement damage are also cumulative effects and mostly affect bulk properties of devices. Their main consequences on the electronic devices are trapping phenomena and the generation of in-gap states.

Firstly all, radiation damage can be fully understood and defined if the information on the incident radiation are known. Among these, there are the particle type (e, p, n,  $\gamma$ , ions, etc.) and energy, the fluence  $\Phi$  or flux  $\phi^1$ , the chances for certain effects occurring (cross section and threshold), and the knowledge of the stochastic or predictable character of the effects. Also, the effects of the radiation depend on the properties of target, such as the chemical composition, the device type (p-n junction, MOSFET, bipolar junction transistor (BJT), etc.), their active volumes and sensitivity. At typical energies involved in HEP radiation environments, ionization is the dominant absorption mechanism and primarily depends on the absorbed energy, independently on the radiation type. Ionization damage is proportional to the energy per unit of mass (dose), usually expressed by gray, 1 Gy = 1 J/kg, or rad, 1 rad =  $6.24 \times 10^{16} \text{ eV/kg}$  (1 Gy = 100 rad). Ionization effects depend on to the target material, since the produced charge by a given dose depends on its electronic properties and crystal structure. Therefore, the ionizing dose must be referred to a specific absorber.

Displacement damage depends on the non-ionizing energy loss (NIEL) [14], i.e., the energy and momentum transferred to the lattice atoms, which exhibits a strong dependency on both particle type and energy. For this reason, the measure of displacement damage must be based on specific particle type and energy.

<sup>&</sup>lt;sup>1</sup>The flux  $\phi$  is defined as the number of particles per unit area and time and the fluence  $\Phi$  is defined as the number of particles per unit area. These two parameters are important in the measure of radiation damage.

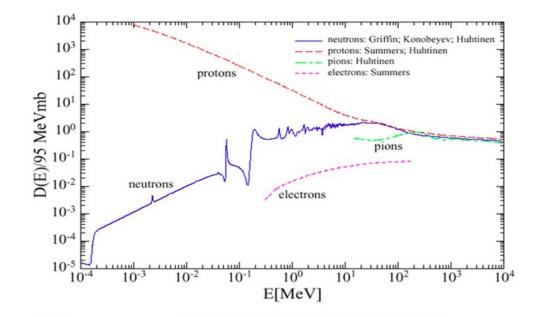

Figure 2.1: Displacement damage in Si as a function of the energy of neutrons, protons, pions, and electrons, normalized to 1 MeV neutrons. [15]

#### 2.2 Total dose-based effects

Firstly, the total dose-based effects will be described. In particular, the main focus will be on phenomena induced by the matter-radiation interaction in MOSFETs and diodes.

#### 2.2.1 Displacement damage

Displacement damage is a complex effect involving a volume or cluster of material atoms rather than a single atom. The extension of the induced defect cluster depends on the incident particles type and energy. For instance, a 1 MeV neutron transfers about 60-70 keV to a Si recoil atom, which in turn displaces roughly 1000 additional atoms in a region of about 0.1  $\mu$ m size. For a variety of particles, NIEL has been calculated over a large energy range. Fig. 2.1 shows the displacement damage integrated in the cross section in Si as a function of the energy for neutrons, protons, pions, and electrons, plotted relative to 1 MeV neutrons. The damage evidently depends on the particle type, with the largest values corresponding to protons at smaller energies than 1 MeV neutrons. Above energy of 300 MeV, the displacement effect for protons, neutrons, and pions is almost the same. However, nor these data neither the induced cluster size and distribution are easy to predict. For example, for 1 MeV neutrons the initial vacancy distribution is highly clustered, whereas for 10 MeV protons the distribution is quite uniformly distributed, and 24 GeV protons form a mixture of clustered and uniformly distributed damage sites [16]. Moreover, the NIEL model allowed to test the radiation resistance of Si compared to other candidates for electronic devices, such as GaAs. The latter is more radiation resistant than Si, except for proton irradiation. Furthermore, it intrinsically shows defects, due to the interface effects of an heterostructure, thus exhibiting several in-gap states favouring trapping phenomena.

The displacement damage can be mainly observed through three effects in the semiconductors, which are listed in the following.

- Formation of in-gap states. The presence of in-gap states favours the electron transition from the valence band to the conduction band, inducing a current enhancement in the reverse-biased *pn*-junctions and a charge loss in forward biased junctions due to the favoured recombination of charge carries.

- **Trapping and detrapping phenomena**. The crystal point defects generate (flat) in-gap electronic states, where some electrons or holes can be attracted getting a localized behaviour. Therefore, trapping and subsequent detrapping effects reduce the system charge mobility or conductivity [17].

- Alteration of the material doping characteristics. The change in donor or acceptor density modifies the doping characteristics of the material, leading to different functionality thresholds.

The silicon band structure exhibits an indirect band- $gap^2$ , so that an inter-band transition without momentum transfer is unlikely.

As anticipated, the in-gap states induce emission and capture processes from the defects. A full understanding of these processes can be achieved by formally defining the ground state of the defected semiconductor. The former consists in fully occupied

$<sup>^{2}\</sup>mathrm{In}$  the Brillouin zone, the valence band maximum and conduction band minimum are related to different Bloch momenta.

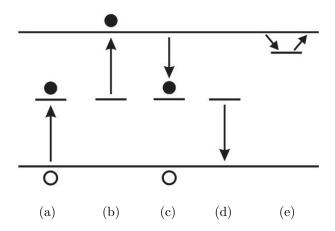

Figure 2.2: Emission and capture processes from a defect level in a semiconducting system involving electrons (filled circles) and holes (unfilled circles). (a) Hole emission, (b) electron emission, (c) electron capture, (d) hole capture, (e) trapping and detrapping. The lower and upper continuous lines represent the valence band maximum and the conduction band minimum, respectively. For each case, the in-gap segment represents the defect energy level. The lack of circles in (d) and (e) indicate that after the process the defect level is unoccupied.

valence bands and a free defect level. In Fig. 2.2, all emission and capture processes from a defect level are reported. Fig. 2.2(a) shows the hole emission process, where an hole is created in the valence band because of the absorption of an electron in the defect level<sup>3</sup> The electron emission process can be only the transition of an electron from the defect level to the conduction band (see Fig. 2.2(b)), since a transition to the valence band would provide a hole capture process. The electron capture process, shown in Fig. 2.2(c), occurs when a conduction band electron is captured in the defect level. The hole capture (see Fig. 2.2(d)) is the transition of the defect level electron to the valence band. Apart from these single-transition processes, the trapping-detrapping phenomenon is a double-transition process occurring when the defect level is sufficiently close to a band edge. In Fig. 2.2(e), the electron trapping is depicted, where a conduction band electron is captured by the defect level and released after a certain time, defined as the trapping relaxation time.

<sup>&</sup>lt;sup>3</sup>Notice that the hole does not move from the defect level to the valence band, since the hole does make physical sense only in the valence band. Here, the emission process for the hole must be intended as a process firstly involving an electron, as well as the capture process will be.

As far as the occurrence of the emission and capture processes is regarded, there are different factors to consider. Firstly, in general, the electronic transition probabilities have the exponential form  $e^{-(E_f - E_i)/k_BT}$ , where  $E_i$  ( $E_f$ ) is the energy of the initial (final) state,  $k_B$  is the Boltzmann factor, and T is the temperature. As a consequence, the existence of electronic (defect) states between the valence band maximum and the conduction band minimum favour the electronic transitions. Also, one should take into account the distance of the defect levels from the band edges, in addition to the distribution of electronic states. Instead, the dominance of generation or recombination process is related to the concentration of carriers and to the empty defect states. In the depletion region of a reverse biased *pn*-junction, the conduction band is underpopulated and the generation prevails. On the contrary, in a forward biased *pn*-junction, the conduction band is largely populated and, thus, the recombination is the prevalent process.

The trapping phenomenon is often observed in radiation detectors and photodiode systems, where the latter imply the decrease of reverse-bias current related to the signal. Such a process decreases the carrier lifetime and, as a consequence, causes a loss of signal, due to the recombination of charge carriers while they traverse the depletion region. The defect states can act as donors, acceptors, or can be electrically neutral. The predominant charge states formed in Si are acceptor-like, and when in sufficient concentration affect the net space charge in the active region [15]. The space charge determines the voltage required for the full charge collection.

#### 2.2.1.1 Displacement damage in diodes

In HEP, reverse-biased diodes with large depletion depths ( $\sim 10^2 \ \mu m$ ) are employed as radiation detectors and photodiodes. The features of the depletion region are strictly related to the bulk properties of the device. Therefore, in reverse-biased diodes, the displacement damage represent the main damage mechanisms, affecting their doping characteristics and influencing the detector leakage current and the charge collection.

The microscopical description of the physical phenomena occurring in the device are quite complex, due to the many processes involved. On the other hand, a macroscopic representation of these phenomena just requires simple parametrizations. The main parameters affected by the displacement damage are the leakage current and the doping characteristics.

The formation of in-gap states in the diode causes an increase of the leakage current. The current after the irradiation depends on the particle fluence  $\Phi$ , the particle type and the active device volume V = Ad, where A and d are the diode area and thickness, respectively. Assuming a spatially uniform formation of active defects in the device volume regardless the details of energy levels and states, the reverse bias current after the irradiation is expressed as

$$I_d = I_0 + \alpha \Phi A d, \tag{2.1}$$

where  $I_0$  is the bias current before irradiation. The factor  $\alpha$  is a damage coefficient expressing the particle type dependency. For instance, the  $\alpha$  value is  $3 \times 10^{17}$  A/cm for 650 MeV protons and  $4 \times 10^{17}$  A/cm for 1 MeV neutrons.

The correct functionality of a diode predicts a current saturation well below the depletion voltage<sup>4</sup>. Instead, in a radiation-damaged diode, the uniform distribution of damage sites provides an initial increase of the leakage current, approximately varying with the square root of the voltage. Afterwards, the current behaviour depends on the annealing process. The latter is a complex process involving system defects, induced by the irradiation and related to the system temperature. The annealing process modulates the migration of radiation-induced defects in semiconducting devices and allows to decrease the leakage current with time after initial defect formation. Furthermore, the reverse bias current is strongly dependent on temperature. As expected, the higher the temperature, the higher the generation current, where the latter is the electrical current generated by the emitted carriers, i.e. the generation current. In particular, even after rather low fluences the generation current dominates and the reverse bias current is

$$I_R \propto T^2 e^{-E/2k_B T},\tag{2.2}$$

where  $E \approx E_g$ , depending on the impurity or defect energy level compared to the band gap value  $E_g$ .

$<sup>^4.</sup>$  The depletion voltage is normally defined as the bias voltage required so that region depleted of free carriers reaches through the whole of the semiconductor bulk REF

As far as the doping characteristic is concerned, in a reverse-biased diode, the n-type region exhibits a positive space charge. After irradiation, the creation of new acceptor states neutralizes the donor states and the positive space charge decreases. A certain value of the fluence implies the absence of the space charge because the new acceptor states balance the old donor states. Beyond this fluence value, a negative space charge is observed because the acceptor states result dominant. Although the diode functionality is unchanged, the bias voltage must be enhanced proportionally to the space charge increase. Indeed, the *n*-type region in a damaged device with *p*-like space charge is not equivalent to a *p*-doped material, since the space charge corresponds to a change in doping level, and the net space charge is an effective doping level  $N_{eff}$ . As a consequence, the needed bias voltage is

$$V = \frac{e}{2\epsilon} \left| N_{eff} \right| d^2, \tag{2.3}$$

where  $\epsilon$  is the semiconductor dielectric constant. In analogy to the conventional diode operation, this is often referred to as the "depletion voltage", although the device is devoid of mobile charge even at smaller voltages [15]. To estimate the value of  $N_{eff}$ , it is needed to consider the contributes of four processes, where the first two represent the "stable damage" contributes because their behaviour is only function of fluence, whereas the other two processes also exhibit time and temperature dependence.

- **Donor removal**. The contribute of donor removal process exponentially depends on fluence.

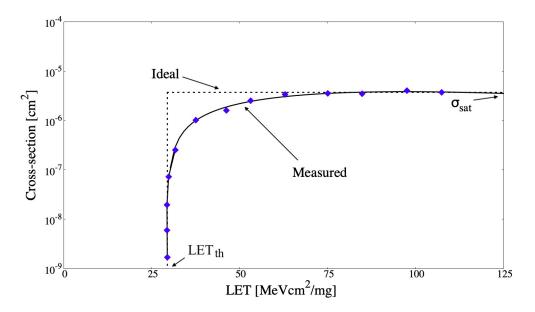

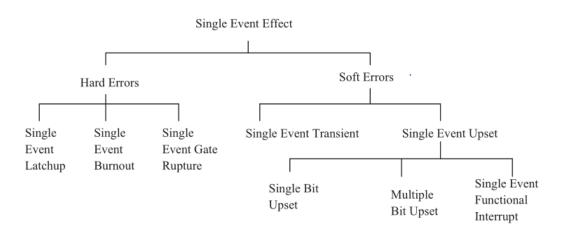

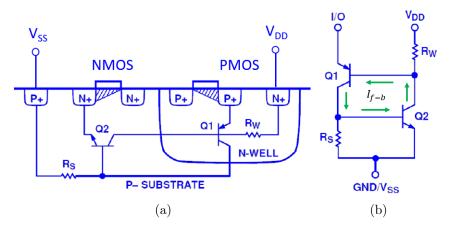

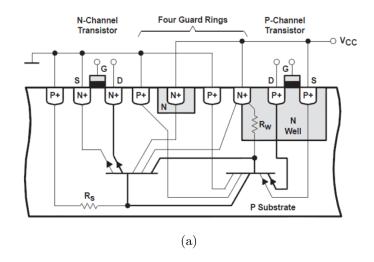

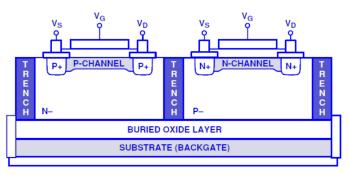

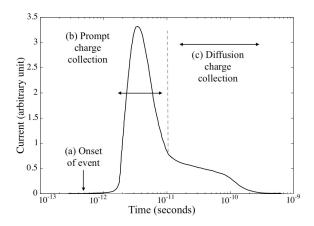

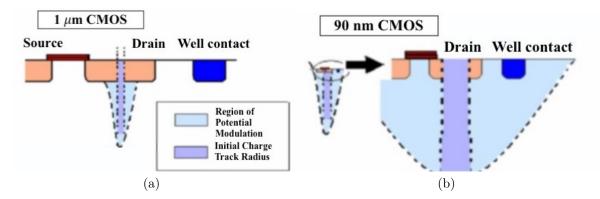

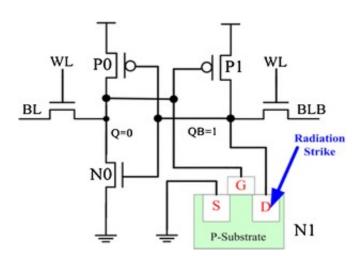

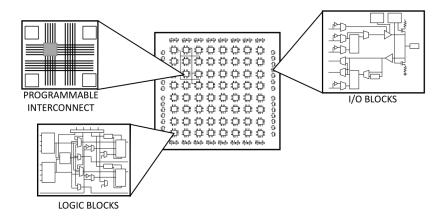

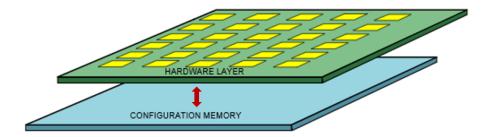

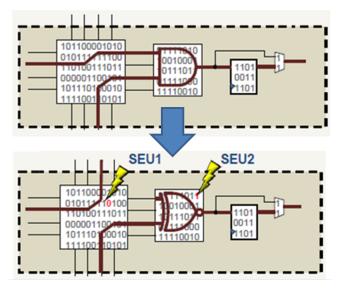

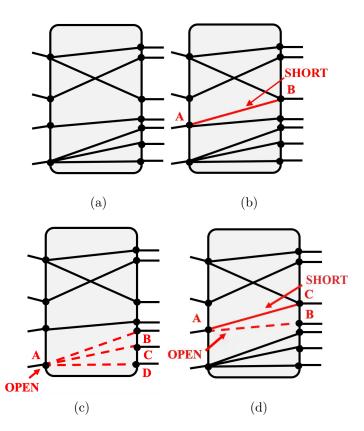

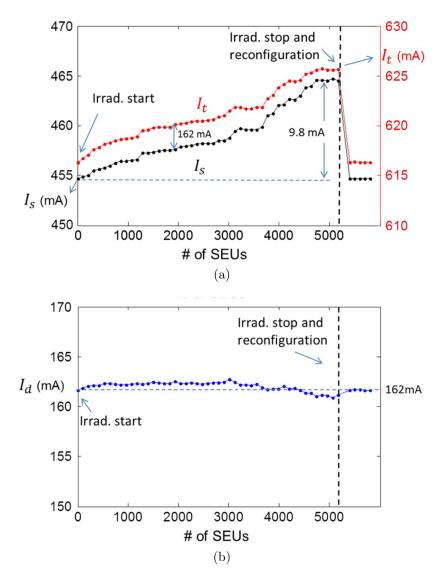

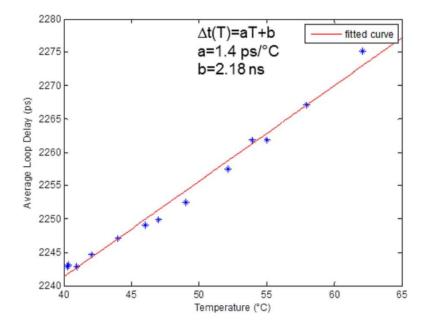

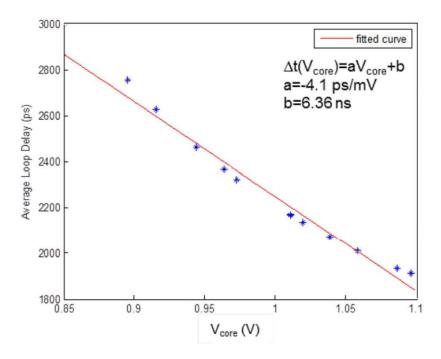

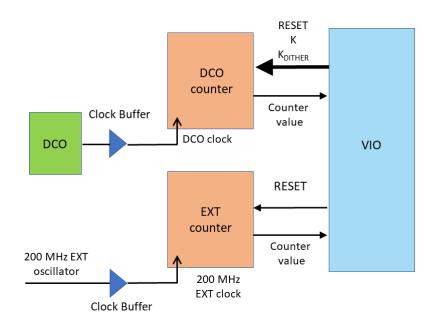

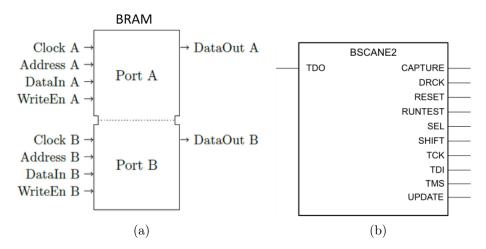

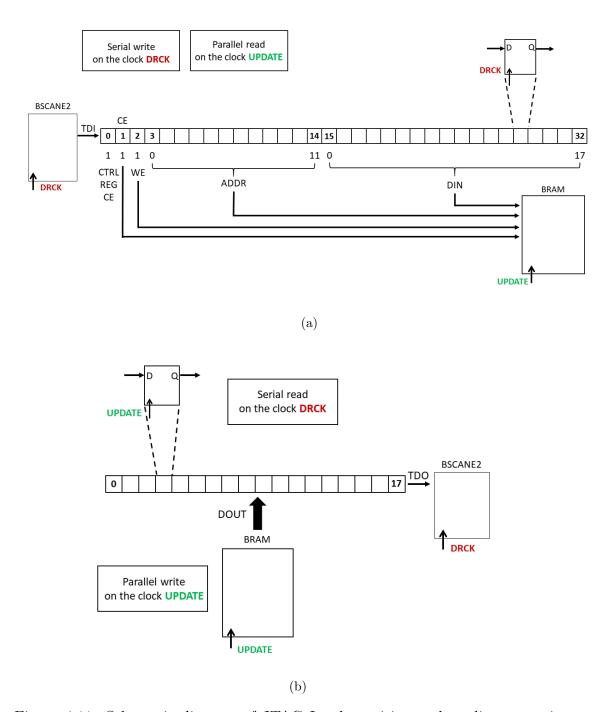

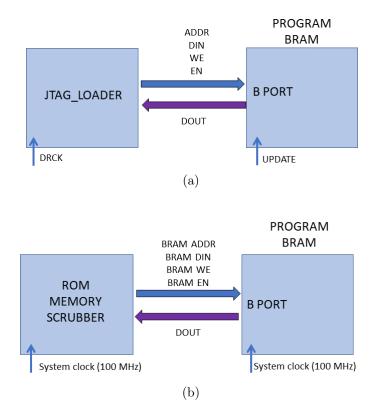

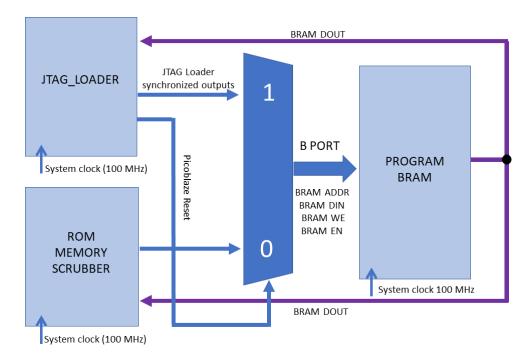

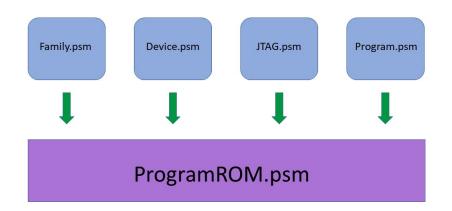

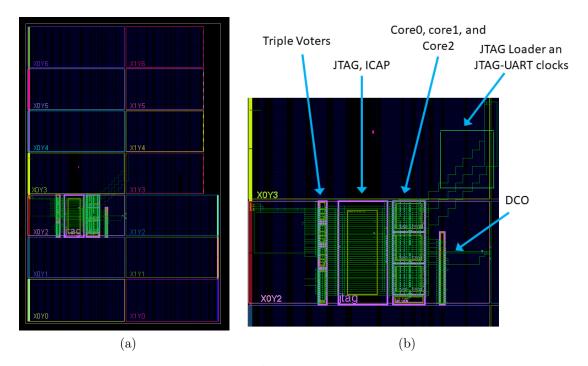

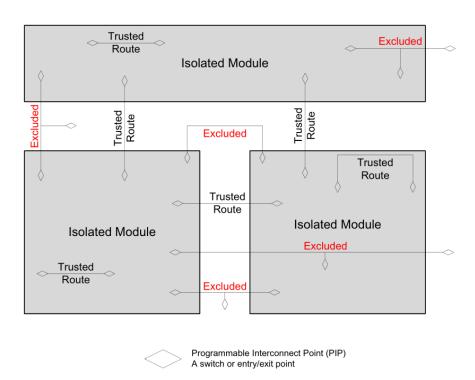

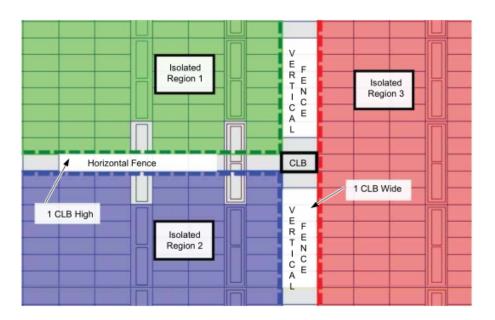

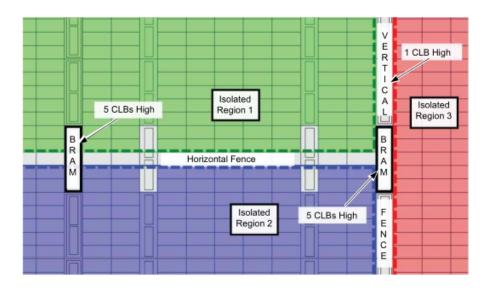

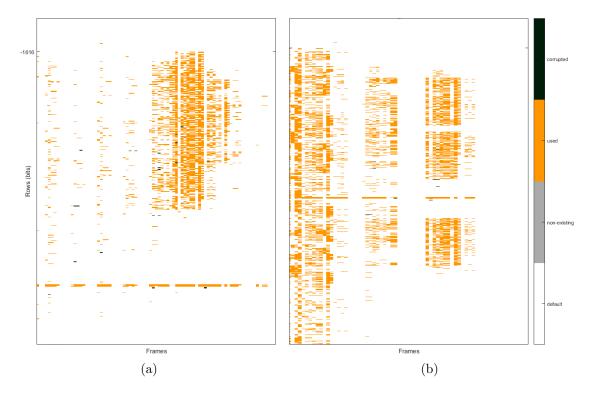

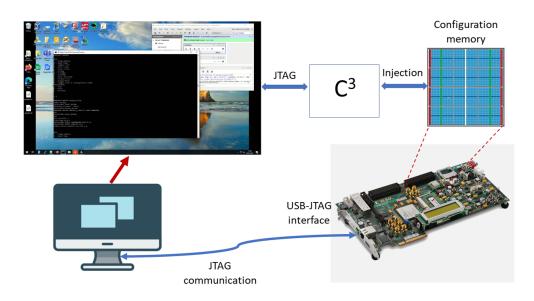

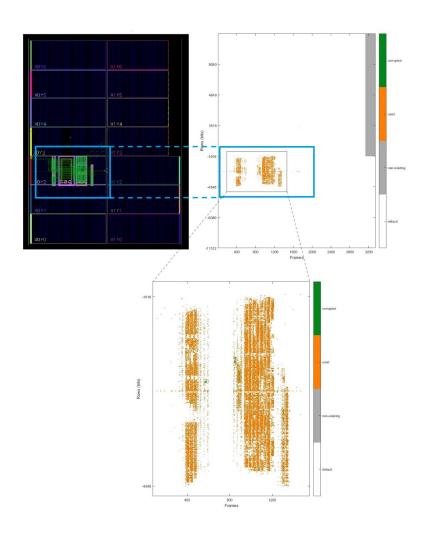

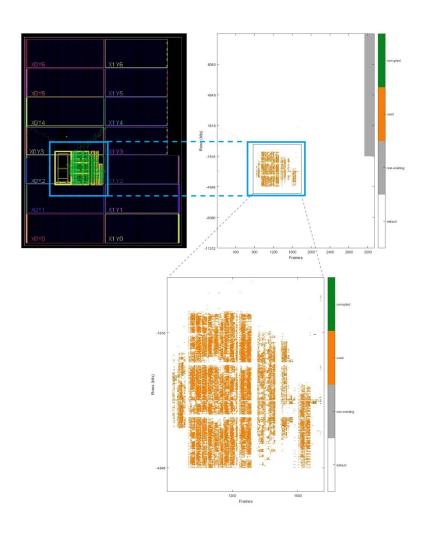

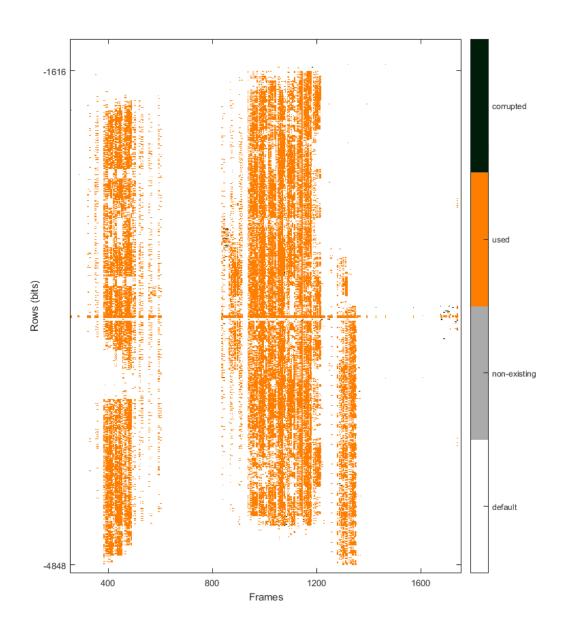

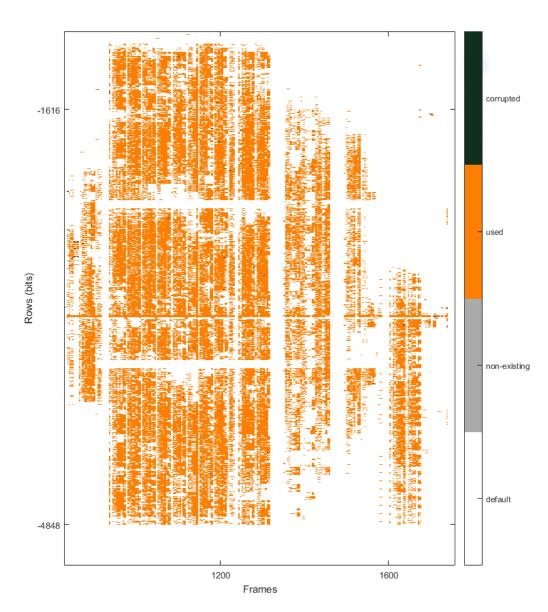

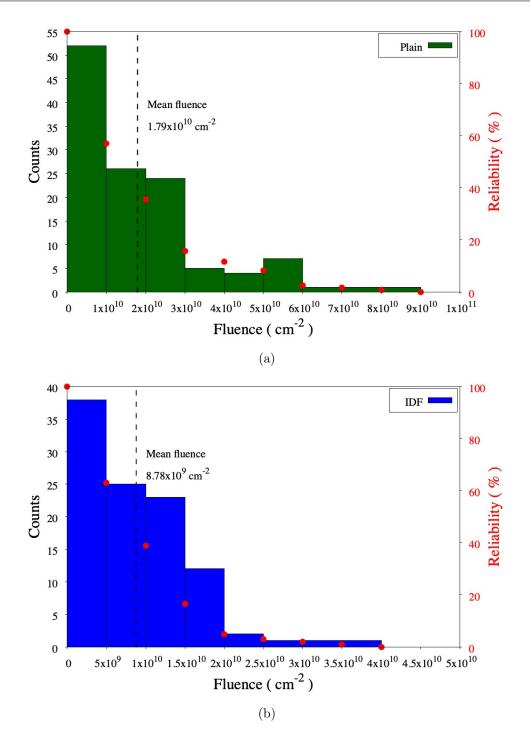

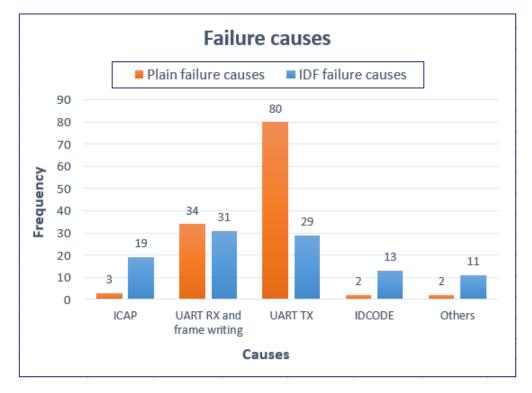

- **Build-up of stable charge**. The contribute of acceptor formation is a linear function of the fluence.