# **Simon Reiter**

Implementation, Operation and Monitoring of the Data Acquisition System of the Belle II Pixel Detector during Physics Data Taking in 2019 – 2022

Dissertation

Implementation, Operation and Monitoring of the Data Acquisition System of the Belle II Pixel Detector during Physics Data Taking in 2019 – 2022

### Implementation, Operation and Monitoring of the Data Acquisition System of the Belle II Pixel Detector during Physics Data Taking in 2019 – 2022

Implementierung, Betrieb und Überwachung des Auslesesystems für einen Silizium-Pixeldetektor am Belle II Experiment während der Datennahme von 2019-2022

Simon Patrik Reiter geboren in Gießen

#### INAUGURALDISSERTATION zur Erlangung des Doktorgrades

am II. Physikalischen Institut des Fachbereich 07 — Mathematik und Informatik, Physik, Geographie der Justus-Liebig-Universität Gießen

(2023)

Dekan: Prof. Dr. Stefan Björn Hennemann Gutachter: apl. Prof. Dr. Jens Sören Lange Gutachter: Prof. Dr. Claudia Höhne

This document was typeset with Lua LTEX 1.17 using the memoir class. The text is set in Libertine, Biolinum, and LibertineMono.

# Selbstständigkeitserklärung

Hiermit versichere ich, die vorgelegte Thesis selbstständig und ohne unerlaubte fremde Hilfe und nur mit den Hilfen angefertigt zu haben, die ich in der Thesis angegeben habe. Alle Textstellen, die wörtlich oder sinngemäß aus veröffentlichten Schriften entnommen sind, und alle Angaben die auf mündlichen Auskünften beruhen, sind als solche kenntlich gemacht. Bei den von mir durchgeführten und in der Thesis erwähnten Untersuchungen habe ich die Grundsätze gute wissenschaftlicher Praxis, wie sie in der "Satzung der Justus-Liebig-Universität zur Sicherung guter wissenschaftlicher Praxis" niedergelegt sind, eingehalten. Entsprechend § 22 Abs. 2 der Allgemeinen Bestimmungen für modularisierte Studiengänge dulde ich eine Überprüfung der Thesis mittels Anti-Plagiatssoftware.

Datum

Unterschrift

# Kurzdarstellung

Die vorliegende Arbeit fasst meinen Beitrag zur Echtzeit-Datennahme des Pixeldetektors des Belle II Experiments am High Energy Accelerator Research Organization (KEK) in Tsukuba, Japan, zusammen. Das Belle II Experiment befindet sich am SuperKEKB Teilchenbeschleuniger, bei dem Elektronen und Positronen mit einer Schwerpunktsenergie von 7.4 GeV aufeinander treffen. Dabei entstehen kurzlebige Teilchen, die nach nur wenigen Mikrometern zerfallen. Aufgrund einer Lebensdauer von teilweise weniger als einer Picosekunde, ist die örtliche Auflösung für die vollständige Rekonstruktion des Zerfalls von entscheidender Rolle. Der Pixeldetektor (PXD), speziell für dieses Experiment entwickelt, besteht aus zwei Lagen, die in einem Abstand von 14 mm und 22 mm zylindrisch um den Wechselwirkungspunkt angebracht sind. Aufgrund der geringen Distanz und der hohen Luminosität von  $6 \times 10^{35}$  cm<sup>-2</sup> s<sup>-1</sup>, werden viele Untergrundsignale erwartet, die nicht für weitere Auswertungen geeignet sind. Durch den langsamen Ausleseprozess von 20 us werden Signale in bis zu 3 % aller Pixel erwartet. Dies entspricht einer Datenrate von über 17 GB/s. Das einheitliche Datennahmesystem aller anderen Detektoren ist dieser Datenmenge nicht gewachsen, so dass an der Justus-Liebig-Universität in Gießen das ONSEN-System entwickelt wurde. Speziell abgestimmte Hardwarekomponenten wurden ausgewählt und in Kooperation mit dem Forschungszentrum IHEP in Peking eine FPGA-basierte Hardware-Plattform entwickelt. Die Firmware des FPGAs ist so konzipiert, dass die Daten mit Hilfe von Bereichen von Interesse reduziert werden, welche durch eine Echtzeit-Ereignisrekonstruktion ermittelt werden. Bevor die Daten gespeichert werden kann so eine Datenreduktion um den Faktor 30 erfolgen. Während der Datennahme wird der PXD sowie alle Komponenten, die für seinen reibungslosen Betrieb notwendig sind, permanent überwacht. Hier kommt eine Software zum Einsatz, die speziell für Physik- und Beschleuniger-Experimente entwickelt wurde. Das Experimental Physics and Industrial Control System (EPICS) zeichnet sich dadurch aus, dass es eine Vielzahl an Geräten unterstützt und das Überwachen und Steuern in einer graphischen Oberfläche dargestellt werden kann.

Dieses Dokument fasst die erfolgreiche Erweiterung des ONSEN-Systems sowie die Integration in das Belle II Experiment zusammen. Die Firmware wurde ergänzt um Überwachungsmechanismen der Datenverarbeitung, um eine reibungslose Datennahme zu gewährleisten und ihre Effizienz zu maximieren. Die kontinuierliche Berechnung der signalgebenden Pixel sowieso die Erkennung von unvollständigen Datensätzen stellten sich als eine der wichtigsten Entscheidungskriterien raus, die zum Bestimmung der Detektorleistung genutzt werden. Der Integrationsprozess umfasste die nahtlose Einbindung der ONSEN-Firmware in EPICS zum Bereitstellen von Echtzeitinformationen. Dies hat sich für die Fehlersuche und den Betrieb als unschätzbar erwiesen, da sie eine rasche Identifizierung und Lösung potenzieller Probleme ermöglicht. Das ONSEN-System hat erfolgreich an der Erfassung von physikalischen Daten teilgenommen und seine Zuverlässigkeit und Robustheit unter Beweis gestellt. Im Laufe von drei Jahren, zwischen 2019 und 2022, hat ONSEN fast 300 TB an Rohdaten zuverlässig analysiert und verarbeitet. In gesonderten Studien wurden Testdaten mit Datenraten von bis zu 4.8 GB/s generiert und unterbrechungsfrei vom ONSEN-System verarbeitet.

Um die Zuverlässigkeit des gesamten PXD zu erhöhen und den aufwendigen Betrieb des Beschleunigers und des Belle II Experiments so effizient wie möglich zu gestalten, wurde die Integration in EPICS des gesamten PXD überprüft. Neben Fehlerbehebung wurden Mechanismen implementiert, um neuen Anforderungen gerecht zu werden, die erst nach Inbetriebnahme ersichtlich wurden. Durch Auswertung von wiederkehrenden manuellen Arbeitsabläufen wurden diese in automatisierte Prozesse überführt, um die Wiederherstellung nach Modulausfällen und die Kalibrierung der Sensoren zu beschleunigen.

## Abstract

This paper summarizes my contribution to the real-time data taking of the pixel detector of the Belle II experiment at the High Energy Accelerator Research Organization (KEK) in Tsukuba, Japan. The Belle II experiment is located at the SuperKEKB particle accelerator, where electrons and positrons collide with a center-of-mass energy of 7.4 GeV. In this process, short-lived particles decay after a few micrometers. Due to a lifetime of sometimes less than a picosecond, local resolution is crucial for the complete reconstruction of the decay. The pixel detector (PXD), specifically designed for this experiment, consists of two layers, spaced 14 mm and 22 mm apart cylindrically around the interaction point. Due to the small distance and the high luminosity of  $6 \times 10^{35}$  cm<sup>-2</sup> s<sup>-1</sup>, many background signals are expected, which are not suitable for further analysis. Due to the slow readout process of 20 µs, signals are expected in up to 3% of all pixels. This corresponds to a data rate of over 17 GB/s. The uniform data acquisition system of all other detectors cannot cope with this amount of data, so the ONSEN system was designed at the Justus Liebig University in Giessen. Specially matched hardware components were selected and an FPGA-based hardware platform was developed in cooperation with the IHEP research center in Beijing. Fine tuned hardware components were selected and an FPGA-based hardware platform was developed in cooperation with the IHEP research center in Beijing. The FPGA firmware is designed to reduce data using regions of interest determined by real-time event reconstruction. Thus, before data is stored, a data reduction by a factor of 30 can be performed. During data acquisition, the PXD and all components necessary for its smooth operation are constantly monitored. Software specially developed for physics and accelerator experiments is used here. The Experimental Physics and Industrial Control System (EPICS) supports a large number of devices and allows monitoring and control information to be displayed in a graphical user interface.

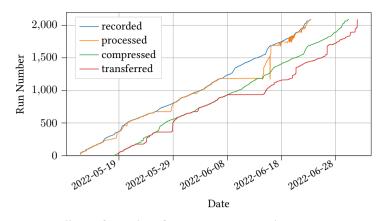

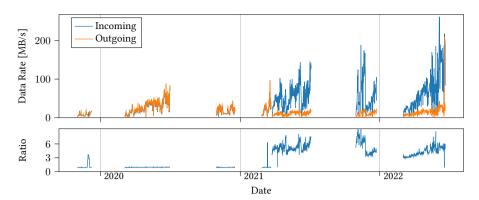

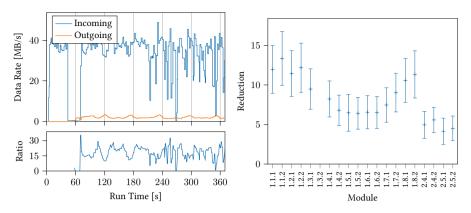

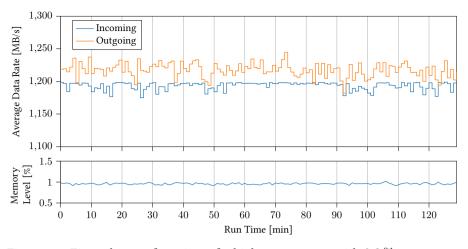

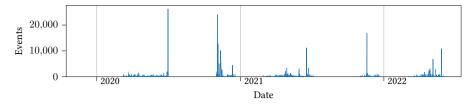

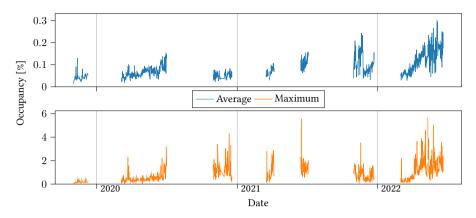

This document summarizes the successful extension of the ONSEN system and its integration into the Belle II experiment. Monitoring mechanisms for data processing were added to the firmware to ensure smooth data acquisition and maximize efficiency. The continuous calculation of signaling pixels and detection of incomplete data sets turned out to be one of the most important criteria used to determine the detector performance. The integration process included seamless integration of the ONSEN firmware into EPICS to provide real-time information. This has proven invaluable for troubleshooting and operations by enabling rapid identification and resolution

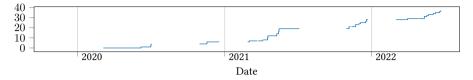

of potential problems. The ONSEN system has successfully acquired physics data, demonstrating its reliability and robustness. Over three years, between 2019 and 2022, ONSEN reliably analyzed and processed nearly 300 TB of raw data. In separate studies, test data with data rates of up to 4.8 GB/s were generated and processed by the ONSEN system without interruption.

To increase the reliability of the entire PXD and to make the operation of the accelerator and the Belle II experiment as efficient as possible, the integration into EPICS of the entire PXD was reviewed. In addition to troubleshooting, mechanisms were implemented to address constraints that became apparent only after commissioning. By evaluating recurring manual workflows, these were transformed into automated processes to speed up recovery from module failures and sensor calibration.

# Contents

| 1 | Introduction               |                                                             |    |  |  |  |  |

|---|----------------------------|-------------------------------------------------------------|----|--|--|--|--|

| 2 | Theoretical Considerations |                                                             |    |  |  |  |  |

|   | 2.1                        | The Standard Model of Particle Physics                      | 3  |  |  |  |  |

|   | 2.2                        | The Standard Model Lagrangian                               | 5  |  |  |  |  |

|   | 2.3                        | CP Violation                                                | 11 |  |  |  |  |

| 3 | The Belle II Experiment    |                                                             |    |  |  |  |  |

|   | 3.1                        | The SuperKEKB Accelerator                                   | 19 |  |  |  |  |

|   | 3.2                        | The Belle II Detector                                       | 21 |  |  |  |  |

|   |                            | 3.2.1 KLM – The $K_L^0$ and Muon Detector                   | 22 |  |  |  |  |

|   |                            | 3.2.2 ECL – The Electromagnetic Calorimeter                 | 23 |  |  |  |  |

|   |                            | 3.2.3 ARICH – The Aerogel Ring-Imaging Cherenkov Detector . | 24 |  |  |  |  |

|   |                            | 3.2.4 TOP – The Time of Propagation Detector                | 24 |  |  |  |  |

|   |                            | 3.2.5 CDC – The Central Drift Chamber                       | 25 |  |  |  |  |

|   |                            | 3.2.6 VXD – The Vertex Detector                             | 25 |  |  |  |  |

|   | 3.3                        | PXD – The Pixel Detector                                    | 26 |  |  |  |  |

| 4 | Data Acquisition 33        |                                                             |    |  |  |  |  |

|   | 4.1                        | Belle II DAQ Overview                                       | 33 |  |  |  |  |

|   |                            | 4.1.1 Trigger System                                        | 33 |  |  |  |  |

|   |                            | 4.1.2 Data Flow                                             | 34 |  |  |  |  |

|   | 4.2                        | PXD Data Handling                                           | 36 |  |  |  |  |

|   | 4.3                        | Online Selection Node                                       | 38 |  |  |  |  |

|   |                            | 4.3.1 Hardware                                              | 40 |  |  |  |  |

|   |                            | 4.3.2 Firmware                                              | 41 |  |  |  |  |

|   |                            | 4.3.3 Software                                              | 46 |  |  |  |  |

|   |                            | 4.3.4 Status                                                | 47 |  |  |  |  |

|   |                            | 4.3.5 Future Development                                    | 48 |  |  |  |  |

| 5 | Slow Control 49            |                                                             |    |  |  |  |  |

|   | 5.1                        | The EPICS Ecosystem                                         | 49 |  |  |  |  |

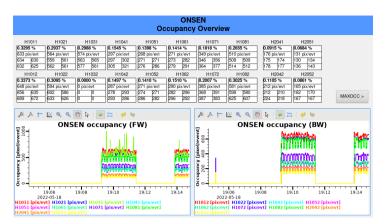

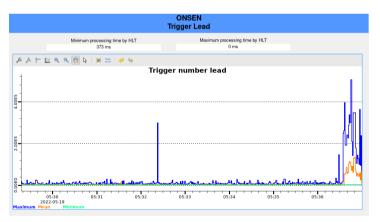

|   | 5.2                        | ONSEN Slow Control                                          | 51 |  |  |  |  |

|   | 5.3                        | ONSEN Run Control                                           | 54 |  |  |  |  |

| References |                      |                |                            |          |  |  |  |

|------------|----------------------|----------------|----------------------------|----------|--|--|--|

| 7          | Summary and Outlook  |                |                            |          |  |  |  |

|            | 6.2                  | Physic         | s Results                  | 84       |  |  |  |

|            | 6.1                  |                | nental Results             | 76       |  |  |  |

| 6          | Ope                  |                | Results                    | 75       |  |  |  |

|            |                      | 5.5.5          | Calibration IOC            | 72       |  |  |  |

|            |                      | 5.5.4          | Data Transfer IOC          | 71       |  |  |  |

|            |                      | 5.5.3          | Local Data Quality Monitor | 70       |  |  |  |

|            |                      | 5.5.2          | Local DAQ Control IOC      | 69       |  |  |  |

|            | 0.0                  | 5.5.1          | PXD Shifter IOC            | 68       |  |  |  |

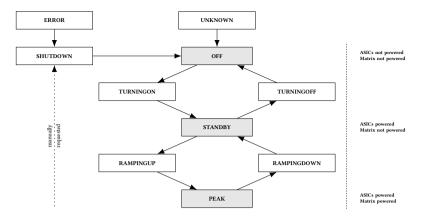

|            | 5.5                  |                | alibration Framework       | 66       |  |  |  |

|            |                      | 5.4.10         | PXD Run Control Update     | 65       |  |  |  |

|            |                      | 5.4.0<br>5.4.9 | PS Sequence Update         | 62       |  |  |  |

|            |                      | 5.4.7<br>5.4.8 | PS Control Update          | 60<br>61 |  |  |  |

|            |                      | 5.4.6          | Clear Channel Handling     | 60       |  |  |  |

|            |                      | 5.4.5          | DHP Register Monitor       | 59       |  |  |  |

|            |                      | 5.4.4          | Test Pattern Upload        | 59       |  |  |  |

|            |                      | 5.4.3          | Module Recovery            | 58       |  |  |  |

|            |                      | 5.4.2          | DHP Link Recovery          | 57       |  |  |  |

|            |                      | 5.4.1          | Overview                   | 55       |  |  |  |

|            | 5.4 PXD Slow Control |                |                            |          |  |  |  |

### Chapter 1

## Introduction

Particle physics experiments are collaborative efforts by researchers investigating nature at small scales. The conduct of an experiment is motivated by a preceding, promising physics theory or exploration of the limits of an established model. The planning and construction of these machines is extremely complex, and experimental physicists design new detectors and, in many cases, dedicated particle accelerators suitable for the task. In order to begin taking data and obtaining long-awaited results, all components of the experiment must be assembled and working, including detectors and data acquisition systems.

There are two types of high energy physics experiments: The ATLAS and CMS experiments at the LHC proton-proton collider utilize large instruments to produce extremely high energy particle beams. Using this method, they can investigate physics processes not possible at lower energies and discover new, very massive particles. In contrast, intensity frontier experiments use very precise detectors and intense particle beams to investigate rare processes. This category includes the Belle experiment at the KEKB electron-positron collider in Tsukuba, Japan.

The Belle experiment concluded in 2010 and plans for an upgrade were approved. This successor Belle II is now the only second generation B-factory. With the upgrade of the experiment comes an upgrade of the KEKB accelerator. The luminosity will be increased by a factor of 30 and a newly developed vertex detector based on a state-of-the-art technology will increase the vertex resolution. This upgrade will amplify the background rate and additional data must be stored.

When the collider reaches its design luminosity, the pixel detector (PXD) will be dominated by background hits and produce data rates of up to 20 GB/s due to the short distance to the interaction point. It was necessary to create a dedicated data acquisition (DAQ) system for the PXD, running concurrently with the Belle II DAQ system, to handle and reduce these high data rates. Therefore the Belle II group at the University of Gießen developed the Online Selection Node (ONSEN) system, using a hardware platform designed at the IHEP in Beijing, China.

The Belle II experiment started operation in 2019, and the ONSEN system proved its capabilities for the first time. This thesis describes the improvement of the firmware and software aspects of the ONSEN system to increase data taking efficiency. Additionally the overall performance of the ONSEN system during the first three years is presented.

For the operation and optimization of the PXD and its accompanying components a sophisticated control and monitoring system is necessary. As part of the thesis to maximize data taking efficiency, system behavior was analyzed in various situations and the software was revised and extended. Individual workflows and handling unpredictable system failures were automated to reduce the downtime.

### **Chapter 2**

### **Theoretical Considerations**

An overview of modern particle physics is provided in this chapter, along with a discussion of the physics of interest to the Belle II experiment. This section describes the forces and particles that make up the *Standard Model* (SM), beginning with an introduction to fundamental particles and their categorization before discussing the most relevant terms of the SM Lagrangian and its implications for *charge conjugation and parity violation*. A brief description of Belle II's method of measuring CP-violations is provided in the second section.

#### 2.1 The Standard Model of Particle Physics

According to current understanding, particle physics examines *elementary particles*, which are nearly point-like objects that cannot be subdivided into smaller components. As a result of Yang and Mills [1], Glashow [2] and Weinberg and Salam's work [3] beginning in the middle of the 20th century, a successful theoretical framework, the Standard Model (SM), has been developed to describe these particles and their interactions in the last decades. With each experimental validation, the SM developed further in the following decades, such as in 1973 when the weak neutral current was discovered [4]. The SM is based on quantum field theories (QFT), theoretical frameworks that combine classical field theories, quantum mechanics, and special relativity. A number of those have been developed on the basis of the two most fundamental QFTs over the past years, quantum chromodynamics (QCD) and quantum field theories with an underlying  $SU(3)_c \times SU(2)_L \times U(1)_Y$  gauge group<sup>1</sup>.

This unified theoretical building is essential to describe three out of the four forces in nature:

<sup>&</sup>lt;sup>1</sup>Here c is the color charge, L the chiral symmetry and Y the hyper-charge. First gauge theory proposed by W. Pauli in 1941 with an invariant Lagrangian under local transformations [5].

#### **Strong Force**

Described by QCD, it contains quarks into proton, neutron, and other hadron particles. It binds neutrons and protons together in atomic nuclei, where it is referred to as the nuclear force.

#### Weak Force

Described by quantum electrodynamics, it is the mechanism of interaction between subatomic particles that are responsible for the radioactive decay of atoms.

#### Electromagnetism

Described by quantum electrodynamics, it governs the interaction between atoms and molecules and occurs when particles with electric charges are in contact with electromagnetic fields.

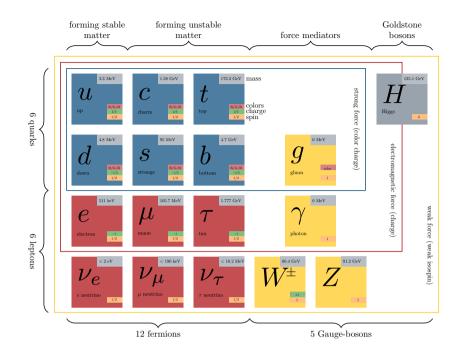

The SM does not describe the most recognizable force, gravitation. As a result of construction, the existence of gravitational force-carrying particles in the Standard Model is valid, but describing phenomena in the Standard Model cannot be accomplished. Due to the small scales and masses resulting from distance and time evolution, gravity is suppressed by many orders of magnitude and may be ignored. It is shown in figure 2.1 how elementary particles and forces are connected in the Standard Model.

In figure 2.1, particles are classified into two kinds. Fermions are particles with spin 1/2 and are responsible for the matter around us. They can be divided into quarks (blue), which carry a color charge and are sensitive to the strong force, and leptons (red). The bosons, on the other hand, have integer spin. Most are resulting from excitations in the associated gauge fields and therefore called gauge bosons (yellow). The strong force is mediated by the gluon (g), the electromagnetic force is mediated by the photon  $(\gamma)$ , and the weak force is carried by the  $W^{\pm}$  and  $Z^{0}$  boson. The SM does not use the Higgs boson ( $\mathcal{H}$ ) to mediate any force, but instead to acquire mass. The Higgs field is responsible for introducing spontaneous symmetry breaking, which is a phenomenon introduced by a complex scalar field that has a non-zero vacuum expectation value in the SM<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>It is the average value that an operator acquires in a vacuum, for example, the state with the lowest energy in the universe.

Figure 2.1: A schematic overview of the fundamental constituents of the Standard Model of Particle Physics.

#### 2.2 The Standard Model Lagrangian

In this section, we will briefly discuss each term of the SM Lagrangian formalism, which is used to represent the mathematical description of the theories unified within the SM.

$$\mathcal{L}_{SM} = \mathcal{L}_{kin} + \mathcal{L}_{EW} + \mathcal{L}_{QCD} + \mathcal{L}_{H} + \mathcal{L}_{YU}$$

(2.1)

In the first term,  $\mathcal{L}_{kin},$  the self-interactions of the gauge bosons are described. It can be written as

$$\mathcal{L}_{kin} = -\frac{1}{4} B_{\mu\nu} B^{\mu\nu} - \frac{1}{2} tr \left( W_{\mu\nu} W_{\mu\nu} \right) - \frac{1}{2} tr \left( G_{\mu\nu} G^{\mu\nu} \right), \tag{2.2}$$

where traces (tr) run over the gauge field tensor of SU(2) and the gluon field tensor of SU(3) indices of W and G respectively.  $B_{\mu\nu}$  represents the gauge field tensor of the weak hyper charge.

Electroweak unification of the SM is described by the second term,  $\mathcal{L}_{EW}$ , which correlates to the symmetry group  $U(1) \times SU(2)_L^{-3}$ .

$$\mathcal{L}_{EW} = \sum_{i} \overline{\psi}_{i} \gamma^{\mu} \left( i \partial_{\mu} - \frac{1}{2} g' Y_{W} B_{\mu} - \frac{1}{2} g \tau W_{\mu}^{a} \right) \psi_{i}$$

(2.3)

A left-handed fermion doublet is depicted as a Dirac spinor in the above equation, which is connected to a vector representation of the Lorentz group by the Dirac matrices  $\gamma_{\mu}$ . As a consequence, the derivatives  $\partial_{\mu}$  introduce a kinetic term for fermions. g' and g are, respectively, coupling constants for electromagnetic and weak fields. The weak hyper charge  $Y_W$  is determined as the generator of the U(1) group acting on the U(1) gauge field  $B_{\mu}$ . It can be related to the electric charge Q and the third component of the weak isospin  $I_3$  by

$$Q = I_3 + \frac{1}{2}Y_W$$

Pauli matrices  $\tau$  act as infinitesimal generators of the SU(2) group and contain the isospin charges of particles interacted with the weak force as their eigenvalues. *Electroweak unification* is achieved by using gauge bosons, in which a weak isospin triplet ( $W^a_\mu$  with a = 1, 2, 3) and a singlet ( $B_\mu$ ) act as mediators between electromagnetic and weak forces [6, 3].

This results in the following couplings for each boson:

#### **photon** ( $\gamma$ )

Are involved in the electromagnetic interaction, since they couple to the electric charge. In the absence of mass and charge, the photon itself becomes the basis for electromagnetic interactions with an indefinite range of application. Neutral particles are not affected.

#### charged $W^{\pm}$ boson

Mediates the charged current of the weak force. Following the SU(2) group, the  $W^{\pm}$  is maximally charged and parity-violating. Therefore, it couples only with left-handed particles and right-handed antiparticles. At present, only the exchange of the  $W^{\pm}$  bosons is capable of a flavor change from up-type quarks to down-type quarks and leptons to its neutrino pair in the SM. Such flavor changes in the lepton sector are limited to individual families. Flavor changes in the quark sector have no such boundaries.

#### neutral $Z^0$ boson

Mediates the neutral current of the weak force. The interaction is similar to the electromagnetic interaction. Since the  $W^{\pm}$  and the  $Z^0$  have very large masses, the weak interaction is short-ranged and has a similar coupling strength

$<sup>^{3}</sup>L$  indicates a coupling only to left-handed fermions, where the spin points in the opposite direction of motion.

to the electromagnetic interaction. For this reason, a flavor change via the neutral current is not forbidden in the SM, but strongly suppressed via the GIM mechanism [6].

The term  $\mathcal{L}_{QCD}$  is introduced in order to describe the strong interactions in the SM.

$$\mathcal{L}_{QCD} = \sum_{j} \overline{\psi}_{j} \gamma^{\mu} \left( i g_{s} G_{A,\mu} T_{A,ij} - m \delta_{ij} \right) \psi_{j}$$

(2.4)

$g_s$  refers to the strong force coupling constant,  $G_{A,\mu}$  refers to the gluon field,  $T_a$  refers to the symmetry generator, and m refers to the mass. There are two indices i and j, which indicate quarks' and gluon's color and anti-color charge. The color charge or only referred to as color is a quantum number, which can be either red, green or blue. Its inverse (anti-color) is also possible for each value. Due to the non-abelian nature of the underlying symmetry group SU(3), gluons always carry color and anti-color at the same time, which allows them to interact with one another. When it comes to quarks, they only carry either color, or anti-color, depending on their type.

The strong force binds elementary particles to hadrons. Depending on their spin they can be classified as mesons with integer spin due to its composition of quark and anti-quark or baryons with half spin<sup>4</sup> composed of 3 (anti-) quarks. The combination of the color of all components is always zero. This behavior is called *confinement* [7, 8] and results in a prohibited observation of colorful particles including unbound quarks. The SM allows bound states with a higher number of constituents. The first observation of such is the X(3872), seen by the Belle experiment in 2003 [9] and later validated by the BaBar and BESIII experiment [10, 11].

As described in the Higgs-term of the Lagrangian, the Higgs-boson contributes kinetic energy to the system along with its interactions with the other force carriers. It can be described like this:

$$\mathcal{L}_{H} = \left[ \left( \partial_{\mu} - igW_{\mu}^{a}t^{a} - ig'Y_{\phi}B_{\mu} \right)\phi \right]^{2} + \mu^{2}\phi^{\dagger}\phi - \lambda(\phi^{\dagger}\phi)^{2}$$

(2.5)

The kinetic term is given by  $\partial_{\mu}$ . The coupling to the weak and electromagnetic force is contributed via g and g'. The Higgs field is the complex scalar  $\phi$ , which is described in the following with superscripts representing the electric charge.

$$\phi = \frac{1}{\sqrt{2}} \begin{pmatrix} \phi^+ \\ \phi^0 \end{pmatrix}$$

The parameter  $\lambda$  and  $\mu^2$  have to be positive to allow spontaneous symmetry breaking.

<sup>&</sup>lt;sup>4</sup>The half spin values follow the formula (2n + 1)/2. No integer spin values are possible.

The last term of the Lagrangian is the Yukawa term. It is responsible for the mass acquisition of quarks. In the equation below  $G_{u,d}$  are  $3 \times 3$  matrices with complex elements each representing the quark generations, where u and d denote up- or down-type quarks. The scalar fields  $\phi$  couple left to right handed quark fields  $D_{L,B}$ .

$$\mathcal{L}_{YU} = G_u^{ij} \overline{U}_L \phi^0 U_R - G_u^{ij} \overline{D}_L \phi^- U_R + G_d^{ij} \overline{U}_L \phi^+ D_R + G_d^{ij} \overline{D}_L \phi^0 D_R \qquad (2.6)$$

Due to the non-zero vacuum expectations on the scalar Higgs fields  $\phi$ , the mass matrices  $(MU_{ij})$  and  $(MD_{ij})$  for up-type and down-type quarks can be expressed as follows:

$$MU_{ij} = \frac{1}{\sqrt{2}} G_u^{ij} v^0$$

and  $MD_{ij} = \frac{1}{\sqrt{2}} G_d^{ij} v^0$  (2.7)

Through diagonalization with the unitarity matrices  $TU_{L,R}$  and  $TD_{L,R}$ , the mass matrices get non-zero entries on their main diagonals. In addition, these matrices transform the weak eigenstate bases of left-handed and right-handed quark fields into mass eigenstate bases. Rather than expressing quark interaction with gauge fields as a weak interaction, the neutral current term remains invariant, while the charge current term changes. GIM is based on this concept, which is why flavor-changing neutral currents are not present at the tree level in SM. The charged currents looks like this:

$$I_{\nu}^{+} = \overline{U}_{L} \gamma^{\nu} D_{L} = \overline{U}_{L}^{M} \gamma^{\nu} T U_{L} T D_{L}^{\dagger} D_{L}^{M}$$

$$I_{\nu}^{-} = \overline{D}_{L} \gamma^{\nu} U_{L} = \overline{D}_{L}^{M} \gamma^{\nu} T D_{L} T U_{L}^{\dagger} U_{L}^{M}$$

(2.8)

As a result of expressing the charged currents in the mass eigenstates (<sup>M</sup>), one can express the transformation matrix  $TU_L TD_L^{\dagger}$  as the Cabibbo-Kobayashi-Maskawa (CKM) unitary matrix  $V_{CKM}$ .

. .

$$V_{CKM} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix}$$

(2.9)

As one observes from comparing the charged current interaction with its charge and parity (CP) conjugated counterpart, the interactions are only equal when

$$V_{CKM_{ij}}^* = V_{CKM_{ij}}$$

is satisfied. The conjugation is made by the exchange of all internal quantum numbers (C) and inversion of the handedness (P). According to Kobayashi and Maskawa, the CKM quark-mixing matrix contains a complex phase when at least three generations

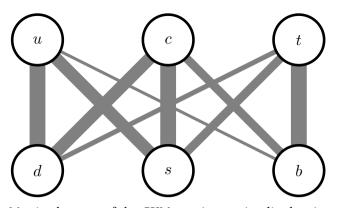

Figure 2.2: Matrix elements of the CKM matrix are visualized as intensity lines between quark families. The thickness correlates to the coupling strength. CKM prefers transitions between quarks belonging to the same family, like u to d and vice versa.

of quarks are present [12]. The result of this phase is that the matrix elements i and j of  $V_{CKM}$  differ from those of  $V_{CKM}^*$ , which constitutes the only source of violation of CP in the SM.

In the CKM matrix, the corresponding matrix element couples the up- and downquarks through charged current interactions mediated by the  $W^{\pm}$  bosons. Feynman diagrams contain matrix elements that describe the strength of the coupling between the charged weak boson and the quark flavors. Figure 2.2 illustrates the strength of this coupling. The coupling strength is indicated by the line thickness between different quark flavors. A higher degree of coupling results in a higher likelihood of a transition occurring. The unitarity conditions the CKM matrix can be expressed like this:

$$\sum_{i} (V_{CKM})_{ij} (V_{CKM})_{ik}^* = \delta_{jk}$$

(2.10)

$$\sum_{j} (V_{CKM})_{ij} (V_{CKM})_{kj}^* = \delta_{ik}$$

(2.11)

These conditions can be combined resulting in six equations that allow a different perception.

$$\begin{split} V_{ud}^*V_{us} + V_{cd}^*V_{cs} + V_{td}^*V_{ts} &= 0\\ V_{ud}V_{cd}^* + V_{us}V_{cs}^* + V_{ub}V_{cb}^* &= 0\\ V_{us}^*V_{ub} + V_{cs}^*V_{cb} + V_{ts}^*V_{tb} &= 0\\ V_{td}V_{cd}^* + V_{ts}V_{cs}^* + V_{tb}V_{cb}^* &= 0\\ V_{td}V_{ud}^* + V_{ts}V_{us}^* + V_{tb}V_{ub}^* &= 0\\ V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* &= 0 \end{split}$$

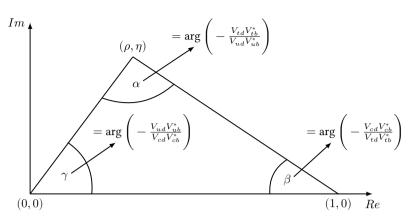

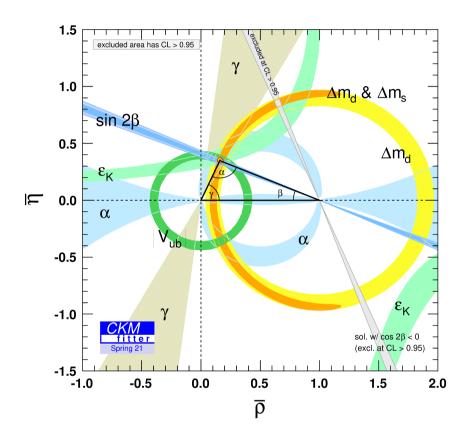

A triangle in the complex plane can be interpreted as a result of all of these equations. It is possible to calculate CP violation in the CKM matrix by measuring the angles of these triangles. In figure 2.2, the coupling strength between quark flavors is represented by lines with different thicknesses. The numerical difference between thick and thin lines is a few orders of magnitude. As a result of the first four equations above, the triangle will appear distorted, with very small angles. Their corresponding decay channels are difficult to measure. In contrast, the last two equations produce triangles with larger angles due to the fact that the matrix elements all have the same magnitude. In *B*-factories like Belle II, where the produced *B* mesons contain a bottom quark, the triangle represented by the last equation contains bottom quark transitions in each terms and is of higher interest. The triangle shown in figure 2.3 highlights some of the measurable decay channels. The angles of the triangle are named alpha, beta, and gamma following the Belle naming scheme and correspond to the matrix elements of the CKM matrix.

$$\begin{aligned} \alpha &= \arg\left(-\frac{V_{td}V_{tb}^*}{V_{ud}V_{ub}^*}\right), \quad \beta = \arg\left(-\frac{V_{cd}V_{cb}^*}{V_{td}V_{tb}^*}\right), \\ \gamma &= \arg\left(-\frac{V_{ud}V_{ub}^*}{V_{cd}V_{cb}^*}\right) \end{aligned}$$

(2.12)

Observable magnitudes can be used as a gauge of the extent of CP violation: No CP violation would result in  $\alpha = \gamma = 1$  and  $\beta = 0$ . On the other hand, CP violation can lead to significant differences between observables. Possible main decay modes for each angle, which can be measured at *B*-factories like Belle II, are

$$\begin{split} &\alpha \!\!: \; B^0 \to \pi^\pm \pi^\mp, \; \rho \pi^0, \ldots \\ &\beta \!\!: \; B^0 \to J/\Psi K^0_S, \; D^* \overline{D}^*, \ldots \\ &\gamma \!\!: \; B^0 \to D^{*\pm} \pi^\mp, \; D^\pm K^\mp, \ldots \end{split}$$

Figure 2.3: The unitarity triangle in the complex plain with its dependency to the CKM matrix elements.

#### 2.3 CP Violation

According to the SM, CP-violations can be classified into two types – direct and indirect. Direct CP violation results in different branching fractions for a particle and its CP conjugated counterpart due to different decay amplitudes. The only source of CP-violation in charged meson decay is this method. A direct CP-asymmetry  $A_{CP}^{dir}$  for charged B mesons can be expressed as the difference in decay rates between  $B^+$  and  $B^-$  normalized to their total decay rate.

$$A_{CP}^{dir} = \frac{Br(B^- \to f^-) - Br(B^+ \to f^+)}{Br(B^- \to f^-) + Br(B^+ \to f^+)}$$

(2.13)

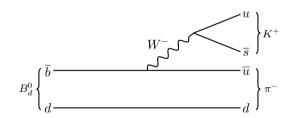

An example for direct CP-violation is shown in the Feynman diagram in figure 2.4.

Figure 2.4: Feynman diagram of the decay  $B^0_d \to K^+\pi^-.$

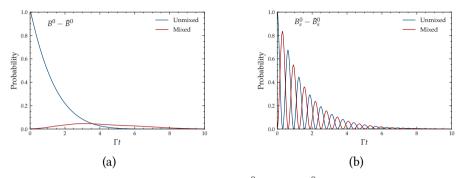

Indirect CP violation occurs as a result of meson mixing. Here a meson containing quark and anti-quark is generated with definite quark flavors, but propagates with distinct mass. It is possible to observe a flavor eigenstate, which is different from the initial flavor eigenstate, after a certain amount of time has elapsed. As a result of this change in flavor eigenstate, the particle oscillates into its own anti-particle and back. As shown in figure 2.5, such oscillation occurs in the mixed system of  $B^0$  and  $B_s^0$ . The mixing frequency is significantly higher in the  $B_s^0$  system due to the stronger CKM-coupling between the *s* and *b* quark. As a result of the flavor change having to skip two generations, the matrix element for  $B^0$  mixing is much smaller.

Figure 2.5: Oscillation probabilities for the  $B^0$  (a) and  $B_s^0$  (b) system in dependence of the decay time t.

The eigenstates of  $B^0$  mixing are differentiated for light (*L*) and heavy (*H*) due to slightly different masses. They are given by

$$B_L = p|B^0\rangle + q|\overline{B}^0\rangle \tag{2.14}$$

$$B_H = p|B^0\rangle - q|\overline{B}^0\rangle \tag{2.15}$$

With the application of the charge operator particles are converted to antiparticles and vice versa. The parity operator introduces a negative sign. The result would look like this:

$$CP(p|B^{0}\rangle + q|\overline{B}^{0}\rangle) = -(p|B^{0}\rangle + q|\overline{B}^{0}\rangle)$$

(2.16)

0

$$CP(p|B^{0}\rangle - q|\overline{B}^{0}\rangle) = (p|B^{0}\rangle - q|\overline{B}^{0}\rangle)$$

(2.17)

These equations can be interpreted that the mass eigenstates are identical to the CP eigenstates. This results in the propagation of a definite CP eigenstate in that state and could not be observed with another value at a later time. To measure a changed value the absolute values of p and q must not be equal. While this violation is only allowed during mixing, it is called *indirect CP violation*.

Another form of direct CP violation can be observed when a particle and its CP conjugate decay to a final state f and the CP conjugated final state  $\overline{f}$ . The magnitude of CP violation is given by

$$\lambda = \frac{q}{p} \frac{A_f}{\overline{A}_f} \tag{2.18}$$

In case of B mesons, while one B can be determined unambiguously, the other B decays into a CP eigenstate. In such case the decay rates can be expressed as

$$f_{\pm}(\Delta t) = \frac{e^{-|\Delta t|/\tau_{B^0}}}{4\tau_{B^0}} \left[ 1 \pm \frac{2\operatorname{Im}\lambda}{1+|\lambda|^2}\sin(\Delta m_d\Delta t) \mp \frac{1-|\lambda|^2}{1+|\lambda|^2}\cos(\Delta m_d\Delta t) \right]$$

(2.19)

Here  $\tau_{B^0}$  is the  $B^0$  lifetime and  $\Delta m_d$  the mass difference between the two B mass eigenstates [13]. The sign for sine and cosine terms is chosen for CP odd final states, for even ones they must be inverted. In order to visualize the possible CP violation, the asymmetry between  $f_{\perp}(\Delta t)$  and  $f_{-}(\Delta t)$  can be constructed.

$$\mathcal{A}(\Delta t) = \frac{f_+(\Delta t) - f_-(\Delta t)}{f_+(\Delta t) + f_-(\Delta t)},$$

(2.20)

which simplifies to

$$\mathcal{A}(\Delta t) = S \sin(\Delta m_d \Delta t) - C \cos(\Delta m_d \Delta t) \tag{2.21}$$

with the amplitudes

$$S = \frac{2 \operatorname{Im} \lambda}{1 + |\lambda|^2} \qquad \qquad C = \frac{1 - |\lambda|^2}{1 + |\lambda|^2}$$

which are related via the following, where  $\theta$  is the phase of  $\lambda$ .

$$\left(\frac{S}{\sin\theta}\right)^2 + (C)^2 = 1$$

After fitting of S and C their values can be related to physical quantities. In case the contributing amplitudes carry the same weak phase the absolute amplitudes  $(\mathcal{A}, \lambda)$  are all equal to 1. Here no CP violation happens and the *mixing induced CP violation* is directly related to the matrix elements of CKM, which are involved in mixing.

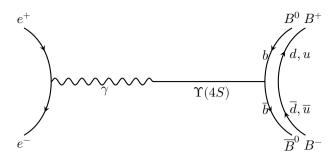

Coherent  $B^0 - \overline{B}^0$  mixing is mandatory for measuring the mixing induced CP violation in B decays at Belle II, thereby allowing to flavor tag a candidate for  $B^0$ . As a result of the production  $e^+e^- \rightarrow \Upsilon(4S) \rightarrow B\overline{B}$ , the B mesons are evolving coherently, starting from a well defined quantum entangled state, and are examples of the Einstein-Podolsky-Rosen [14] effect as shown in figure 2.6. The  $e^+e^-$  collision at Belle II produces a virtual photon which forms as  $\Upsilon(4S)$  due to total energy of the collision being exactly the mass of the B meson. The energy is chosen to be the first bottomonium state above the open B threshold, resulting in decays from  $\Upsilon(4S)$  to B mesons in 96 % of all decays.

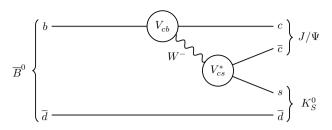

In order to tag the flavor, one of the two B mesons must decay into its final state. Figure 2.7 illustrates such a decay. The tagged B meson decays via semileptonic decay. Due to the quantum entangled B system, the other B meson from

Figure 2.6: Production of B mesons at the SuperKEKB accelerator via a virtual photon and the bottomonium state  $\Upsilon(4S).$

the production via  $\Upsilon(4S)$  must be the anti-particle at the time of the decay. The shown decay  $B^0 \to D^- l^+ \nu_l$  is flavor specific only for the  $B^0$ . While the other B meson continues to propagate, its flavor oscillates until it decays either as  $B^0$  or  $\overline{B}^0$ . A CP violation can be measured in interference between decay and mixing if the decay happens to be an eigenstate of CP, as in the example of  $J/\Psi K_S^0$ . The article by Bigi and Sanda [15] concluded that the decay is an excellent candidate for measuring time-dependent CP violations for the  $\beta$  angle (shown in figure 2.3), as it is often referred to as the *golden channel* (see figure 2.8). It is crucial to know the difference in decay times  $\Delta t$  between the two decays of the B mesons in order to determine time-dependent CP violations. It is important to note that in the production process, the B mesons are produced at rest, provided that the  $\Upsilon(4S)$  has momentum zero. In this case it is not possible to measure a decay time difference.

Figure 2.7: Schematic of the flavor tagging decay process. In the boosted  $e^+e^-$  rest frame an  $\Upsilon(4S)$  is produced and decays immediately into two *B* mesons. With one *B* meson decaying via its flavor specific channel, the other *B* meson decays later into a CP eigenstate.

In order to produce  $\Upsilon(4S)$  with a non-zero momentum, the kinetic energies of the electron and positron beams must be asymmetric. As show in figure 2.7 by

Figure 2.8: Decay of  $\overline B{}^0 \to J/\Psi K^0_S,$  referred to as golden channel.

the different length of the dashed arrows, this mechanism is also used by Belle and Belle II. The electrons are stronger accelerated, such that one can calculate the time difference by

$$\Delta t = \frac{\Delta z}{\beta \gamma c}$$

Here  $\beta\gamma$  is the boost of the center of mass frame, c the speed of light and  $\Delta z$  the vertex shift between the decay of two B mesons in beam direction. With the upgrade of the Belle experiment the silicon-strip vertex detector is replaced in the most inner layer by a pixel detector. This decreases the vertex resolution in z direction from roughly 100 µm down to 20 µm. Further details of the Belle II experiment will be discussed later in chapter 3.

The first measurement of the *golden channel* by Belle and BaBar collaborations were published in 2001 [16, 17]. The measured time-dependent CP violation in the *B* meson system is based on the mixing-asymmetry parameter

$$\frac{q}{p} = \frac{V_{td}V_{tb}}{V_{td}^*V_{tb}} \quad . \tag{2.22}$$

With equation (2.18) the connection to the coefficients q and p can be established. With the dominant decay to  $J/\Psi K_S^0$  the decay amplitudes can be written as

$$\frac{A_f}{A_f} = \eta_f \frac{V_{cb} V_{cs}^*}{V_{cb}^* V_{cs}} \frac{V_{cs} V_{cd}^*}{V_{cs}^* V_{cd}} \quad , \tag{2.23}$$

where  $\eta_f$  is the CP eigenvalue of the final state. For the decay  $J/\Psi K^0_S$  the eigenvalue is -1, but for  $J/\Psi K^0_L$  it is +1. The mixing parameter  $\lambda$  can not be written as

$$\lambda = \eta_f \frac{V_{td} V_{tb}^*}{V_{td}^* V_{tb}} \frac{V_{cb} V_{cd}^*}{V_{cb}^* V_{cd}}$$

(2.24)

using the definitions of the angles of the unitarity triangle (equation (2.12))

$$=\eta_f e^{-2i\beta} = \eta_f \cos(2\beta) - i\eta_f \sin(2\beta) \quad . \tag{2.25}$$

The asymmetry amplitudes can be calculated to be

$$C = \frac{1-|\lambda|^2}{1+|\lambda|^2} = 0 \qquad \qquad \text{and} \qquad \qquad S = \eta_f \sin(2\beta) \quad,$$

where the term of the direct CP violation C vanishes and the mixing term S remains. With the previous definition of the asymmetry in equation (2.21), one now can express the time-depended CP violation as

$$\mathcal{A}(\Delta t) = \eta_f \sin(2\beta) \sin(\Delta m_d \Delta t) \quad . \tag{2.26}$$

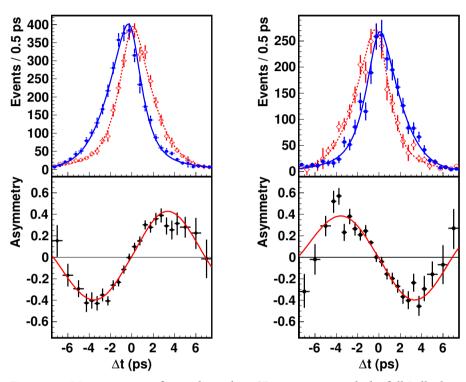

In equation (2.26) the amplitude  $\mathcal{A}(\Delta t)$  and the second sine term can be measured and  $\eta_f$  is defined by the final state of the kaon. The first sine term and therefore also the  $\beta$  angle of the unitarity triangle can be determined. In figure 2.9 the analysis of the full Belle data set of 711 fb<sup>-1</sup> is shown.

Over the last decades more results have been published and the CKM-fitter group provides fitted values. In figure 2.10 the latest results from 2021 are shown. The most recent values of the Wolfenstein parametrization [18] are listed below:

| $\mathcal{A} = 0.8132^{+0.0119}_{-0.0060}$    | $\lambda = 0.22500^{+0.00024}_{-0.00022}$          |

|-----------------------------------------------|----------------------------------------------------|

| $\overline{ ho} = 0.1566^{+0.0085}_{-0.0048}$ | $\overline{\eta} = 0.3475  {}^{+0.0118}_{-0.0054}$ |

The angles of the unitarity triangle are

$$\alpha = 91.98^{\circ} {}^{+0.82}_{-1.40} \qquad \beta = 22.42^{\circ} {}^{+0.64}_{-0.37} \qquad \gamma = 65.5^{\circ} {}^{+1.3}_{-1.2}$$

Figure 2.9: Measurements of time-dependent CP asymmetry with the full Belle data set [19]. The left plot shows the CP-odd final state via decay  $B \to K_S^0 J/\Psi$ . The right plot shows the CP-even final state via  $B \to K_L^0 J/\Psi$ . The upper plot shows the decay rates in each case, with  $B_{tag} = B^0$  in red and  $B_{tag} = \overline{B}^0$  in blue. In the lower plots the asymmetry is calculated, which allows the extraction of  $\sin(2\beta)$ .

Figure 2.10: The global CKM fit in the large  $(\overline{\rho}, \overline{\eta})$  plane as a graphical representation of the unitarity triangle. The color areas indicate the error bars. Plot provided and updated by the CKM-fitter group [20].

### Chapter 3

## The Belle II Experiment

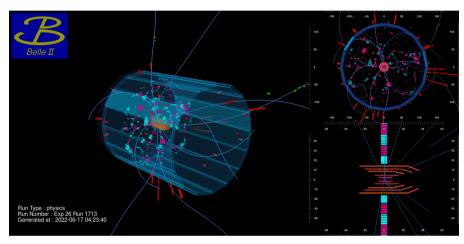

The following chapter describes the basics of the Belle II experiment, its attached accelerator facilities and gives an overview of the single components of the detector. Further the pixel detector is described in more detail with focus on the data acquisition system.

#### 3.1 The SuperKEKB Accelerator

SuperKEKB is an upgraded version of the former KEKB collider that provided beams for the Belle experiment. As the name indicates, SuperKEKB is located in KEKB's same tunnel and uses many of its old components. The principal enhancement, compared to its predecessor, is the increase by 30 in design luminosity. In this way, Belle II will be able to collect data of approximately  $50 \text{ ab}^{-1}$ . This section provides a brief overview of the main changes required to meet upgrade specifications. A more detailed description can be found in the technical design report [21].

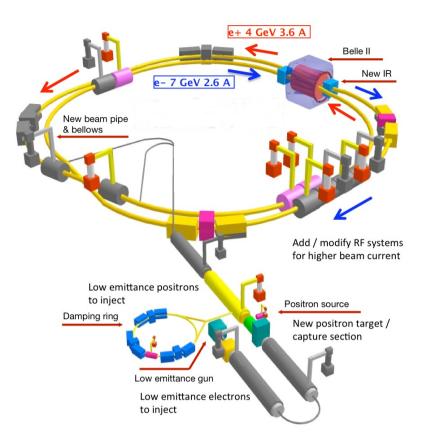

Figure 3.1 illustrates the SuperKEKB accelerator. It is an asymmetric collider and its rings are referred to as the Low-Energy Ring for positrons (LER) and the High-Energy Ring for electrons (HER), each with a circumference of 3016 m. The different energies for electrons (7 GeV) and positrons (3.6 GeV) result in a boosted center of mass system in order to identify displaced vertices of *B* mesons. The boost is decreased from  $\beta \gamma = 0.48$  down to  $\beta \gamma = 0.28$  due to higher beam currents. This change requires compensation by an upgraded vertex detector scheme of Belle II using a combination of silicon strips and pixels.

A damping ring is used to increase the emittance of positrons by a factor of 2, as their emittance is not small enough to satisfy the injection requirement. As part of the production process, a radio frequency (RF) gun is used to irradiate a photo cathode with laser photons pulsed at short intervals. After acceleration to 7 GeV in the linear accelerator, they are dumped into the HER. The KEKB thermionic RF electron gun is used for positron production. After being fired at a tungsten target at 3.3 GeV and causing bremsstrahlung, an electron-positron pair is produced. As a result of this procedure, a high emitting positron beam is accelerated to a velocity

Figure 3.1: Sketch of the SuperKEKB accelerator facility.

of 1 GeV and directed to a damping ring, which reduces the emittance and further accelerates the positrons to 4 GeV before being stored in the LER.

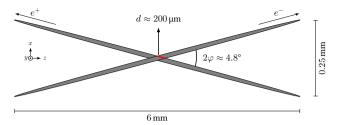

A significant upgrade to achieve the designed luminosity is the *nano-beam scheme*, which is illustrated in figure 3.2. This technique allows to reduce the vertical beam size at the interaction point by a large amount, thus increasing the luminosity. For two flat beams of equal size, the luminosity is defined in the following manner.

$$\mathcal{L} = \frac{\gamma_{\pm}}{2er_e} \frac{R_L}{R_{\zeta_u}} \frac{I_{\pm}\zeta_{y,\pm}}{\beta_{y,\pm}^*}$$

(3.1)

Here  $\gamma$  is the Lorentz factor, e the electron charge and  $r_e$  the classical electron radius.  $R_L$  and  $R_{\zeta_y}$  are reduction factors for the luminosity. They depend on the crossing angle and are of the same magnitude. Adjustable parameters are the beam current I, the vertical beta function  $\beta_u^*$  at the interaction point and the vertical beam-beam

Figure 3.2: An illustration of the collision of beams in the nano-beam scheme. Only the overlap region d is taken into account instead of the much larger bunch length  $\sigma_z$ .

parameter  $\zeta_{n,+}$ . The beta function is directly connected to the vertical beam size by

$$\sigma_y = \sqrt{\epsilon \beta_y^*} \tag{3.2}$$

Using quadrupole magnets along the beam pipe, the beam is squeezed, and a final focusing magnet (QCS) reduces its vertical beta function to  $\beta_y^* = 270 \,\mu\text{m}$  for the LER and  $\beta_y^* = 410 \,\mu\text{m}$  for the HER, thereby reducing the vertical beam size significantly. With this method, luminosity cannot be increased arbitrarily and is always constrained by bunch length  $\sigma_z$ , thereby introducing a hard limit of 5 mm in beam direction. By using a finite beam crossing angle  $2\phi$ , the nano-beam scheme corrects for this effect, resulting in a decrease in the effective cross section of the beams of  $d = \sigma_x/\phi$  with  $\sigma_x$  representing the horizontal beam spread. The beta function is constrained by

$$\beta_u^* > d$$

With a half crossing angle of  $\phi = 41.5$  mrad and a horizontal beam size of  $\sigma_x = 7.75 \,\mu\text{m}$ , the effective crossing length is  $d = 200 \,\mu\text{m}$ , which corresponds to a 25-fold smaller constraint than the 5 mm provided by the bunch length. SuperKEKB will be able to reach its design luminosity goal with the nano-beam scheme of

$$\mathcal{L} = 6 imes 10^{35} \, \mathrm{cm}^{-2} \, \mathrm{s}^{-1}$$

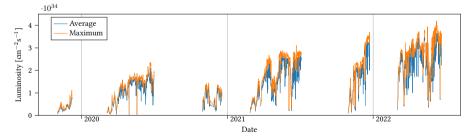

This instantaneous luminosity will be 30 times higher than the Belle luminosity record from 2009 of  $2.11 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> [22] and the total integrated luminosity is expected to reach  $50 \text{ ab}^{-1}$  by a similar run time. The most recent SuperKEKB luminosity record of  $4.71 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> was reached in June, 2022 [23].

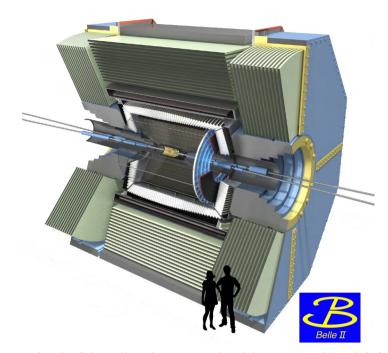

#### 3.2 The Belle II Detector

The Belle II detector is placed around the crossing of the two beams, where particles interact with each other. The detector is a construct of multiple layers housing different subdetectors in order to determine energy, position and time. Each subdetector

Figure 3.3: Sketch of the Belle II detector. Each subdetector is colorized differently. From the outmost KLM in green, followed by the solenoid coil and the ECL in white, the ARICH in blue tiles in the forward region, the TOP as transparent slabs, the CDC as grey long strips and the VXD, which is in yellow for the SVD and in red for the PXD subsystem.

has its own purpose and is placed in a barrel shape around the interaction point or at an end-cap to maximize the acceptance. Acceptance ranges from 17° to 150° in the azimuthal plane and the entire angular range is covered in the polar plane. The higher acceptance in the forward direction is necessary, because particles are boosted into this direction by different beam momenta. The outer subdetectors are responsible for particle identification, the inner ones mainly focus on track reconstruction. In the following a summary of each subdetector is given starting from the most outer ones.

### 3.2.1 The $K_L^0$ and Muon (KLM) Detector

The outermost detector focuses on the detection of long living particles, which propagate easily through detector material. For B decays the neutral kaon  $K_L^0$  is the most reasonable candidate passing next to muons. Without carrying electrical charge there is no reason to keep the detection of those within the homogeneous magnetic field, therefore the  $K_L^0$  and muon detector is the only one of the barrel subdetectors, which is placed outside of the superconducting solenoid, but still inside the magnetic yoke.

There are multiple layers of glass-electrode resistive plate chambers (RPCs) [24], which were already used in Belle, and of iron plates arranged in alternating order.  $K_L$  mesons with a minimum momentum of  $\sim 0.6$  GeV/c (or  $\sim 1.5$  GeV/c depending on their polar angle) will most likely interact in the iron plates and create hadronic showers. Due to a high dead time of the RPC, the detection is adversely affected with higher beam background. Especially in the end-cap regions with limited neutron shielding the background is not acceptable anymore and the RPC layers are replaced by organic scintillator strips [25].

The RPC consists of two float glass layers conducting electricity although they are high electrical resistive. Separated by plastic spacers they are applied with high voltage using a carbon-doped paint and the remaining gap is filled with a gas mixture. Passing charged particles ionize molecules and a streamer formation is enforced by the accelerated electrons in the strong electric field. The streamer formation serves as a conducting channel allowing charge to flow from one plate to another. The high resistive glass limits the size of this local discharge, which itself reduced the electric field and counteracts the streamer formation. With external pickup strips, each with a width of 5 cm, the streamer formation can be transmitted via these strips to discriminators and serializers. Since the strips are mounted on the ground plane of both sides each signal can be detected twice, resulting in a redundant detection.

In the end-cap superlayers of organic scintillators strips are used to handle the higher particle flux mainly caused by background events. The scintillation light is transported by wavelength shifting fibers to photomultipliers, where the signal is converted by frontend electronics.

In order to distinguish muons from charged hadrons, the range of a track whose momentum is the same in the KLM is determined. KLM hits that correspond to muon tracks are used to identify muons in the CDC. Observed and predicted muon ranges are compared to estimate muon likelihoods. False positives are mostly misidentified charged pions, while  $K_L^0$  are identified by hits in KLM that do not correspond with CDC tracks. Neither ECL nor KLM can initiate hadronic showers.  $K_L^0$  candidates must have at least two clusters projecting roughly to the interaction point, where one of them must be in KLM and the second one either in KLM or ECL. A rough momentum reconstruction for the  $K_L^0$  is possible with information obtained from KLM time-of-flight measurements.

## 3.2.2 The Electromagnetic Calorimeter (ECL)

As a result of *B* meson decays, approximately 3% of the final state products are neutral particles such as pions, kaons, and photons. These produce a large number of photons with energies ranging from 20 MeV to 4 GeV. Consequently, a highresolution *electromagnetic calorimeter* [26] is an integral part of the Belle II's particle identification. The majority of ECL components have been reused from Belle, while only the readout system has undergone significant changes. For the detection, scintillating cesium-iodide crystals doped with thallium CsI(TI) are used. They are read out by photodiodes and digitized by flash ADCs as part of the detection process. For the end-caps, pure CsI crystals will be installed to overcome the more severe background environment. In Belle II, ECL is constructed of 8736 crystals, 1216 of which are in the forward region and 1040 in the backward region. In addition to its primary task, the detection and differentiation of electrons and photons, it also serves as the primary trigger source for Belle II. The energy resolution is expected to be

$$\frac{\sigma_E}{E} = \sqrt{\left(\frac{0.066\,\%}{E/{\rm GeV}}\right)^2 + \left(\frac{0.81\,\%}{\sqrt[4]{E/{\rm GeV}}}\right)^2 + (1.34\,\%)^2}$$

## 3.2.3 The Aerogel Ring-Imaging Cherenkov (ARICH) Detector

On the forward end-cap inside the ECL is located the Aerogel ring-imaging Cherenkov detector [27]. A 4 cm thick Aerogel radiator is arranged in a radial structure divided into hexagonal tiles at a distance of 167 cm from the interaction point, covering an angle of 14° to 43°. The radiator consists of 2 pads of the same thickness but with different refractive indices (1.055 and 1.065). This way photons produced in the second pad have a larger Cherenkov angle and exactly overlap with in the detector, which provides a better signal yield. 540 hybrid avalanche photo detectors (HAPDs), each divided into 12 × 12 matrices and placed 20 cm from the outer Aerogel layer, detect the light produced.

## 3.2.4 The Time of Propagation (TOP) Detector

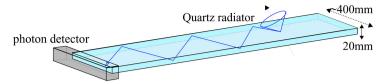

For the barrel, particle identification is done by an *imaging time of flight* detector [28]. It consists of 16 quartz radiator bars of size 2.7 m by 0.45 m with a thickness of 20 mm. A prism is positioned at the reflective edges of each quartz bar to increase the detectable area to 51 mm, as shown in figure 3.4. All borders of these bars, with the exception of one, completely reflect the Cherenkov light emitted by particles traversing the quartz. For detection, 32 micro-channel plate photomultiplier tubes (MCP-PMTs) are arranged in two rows at the prism. Cherenkov light is reflected towards the detection end by a mirror attached to the opposite side of the quartz. By measuring the time between bunch crossing and Cherenkov light detection with the MCP-PMTs, 50 ps time resolution is possible. As a result, the particle travel time to the detector is added together with the propagation time of Cherenkov light in quartz to determine this time. It is possible to calculate the position and angle of the particle when it hits the TOP-quartz by comparing the Cherenkov information with the tracking information. This outcome is compared with a predicted particle, based on the premise that the particle is either a kaon or a pion, which provides the probability of the measured particle being found. It is calculated and associated with the particle candidate in the final reconstruction.

Figure 3.4: Schematic overview and the concept of the TOP counter. A quartz radiator propagates Cherenkov light, which is detected at the bar end by a photon detector.

## 3.2.5 The Central Drift Chamber (CDC)

As the outermost tracking detector, the Central Drift Chamber [29] consists of 14366 sense wires divided into eight super layers that alternate between each other. There are six sense wire layers in each super layer (the innermost layer has eight) arranged in axial layers parallel to the beam pipe, and stereo layers tilted between  $-74^{\circ}$  and  $70^{\circ}$ . In the CDC volume that extends from  $160\,\mathrm{cm}$  to  $1130\,\mathrm{cm}$  in radial direction and 2.4 m in beam direction, helium and ethane are mixed. By traversing the CDC with a curved trajectory, charged particles ionize this gas. The electric field between the wires causes liberated electrons to drift towards the sense wires, which produces an electrical signal. The distance between the origin and the particle trajectory can be calculated based on the signal timing and drift velocity. The trajectory can be fitted as a circle in the plane perpendicular to the beam pipe. To obtain the slope of the typical track-helix, stereo wires have been used. Due to the bending radius of charged particles in magnetic fields, the CDC can determine their momentum. Another key value, determined by the CDC information, is the energy loss per length dE/dx. By ionizing the gas, particles deposit a small amount of energy in each layer when passing through the CDC. It is possible to calculate the energy loss based on the mean energy loss along the particle's trajectory. The correlation between momentum and energy loss is used to separate particle types.

## 3.2.6 The Vertex Detector (VXD)

As mentioned earlier, the inner tracking detector is divided into 2 completely different subdetectors. The output part of the vertex detector uses the same detection technique as in the predecessor experiment with some improvements. This *silicon vertex detector* (SVD) [30] consists of four layers of silicon strip sensors mounted on ladders. The sensors consist of a p-doped strip in beam direction, a n-doped strip perpendicular to it, separated by an n-doped bulk region, which is ionized by traversing charged particles. During ionization of bulk silicon, electron-hole pairs are formed, and electrons and holes drift towards their charged conjugated strip. Those strips are read out by an external trigger signal, which is sent from the global data acquisition system. A special CMOS-based front-end chip APV25 [31] on the sensor amplifies the signals and transmits them to the flash ADC, which is located outside of highly radiative areas. As the analog signals are shaped and digitalized by the flash ADC, they are transmitted over an optical data link to the global data acquisition system.

Figure 3.5: A 3D model of the SVD. In boost direction the sensor have a wedge shape in order to increase the angular coverage to 17°.

In silicon strip detectors, there is a common geometrical problem associated with their configuration. The detector produces ghost hits as a result of the perpendicular arrangement of the strips. Ghost hits are naturally produced when charged particles cross the detector. Therefore, if a certain number of particles cross the detector at the same time, the same amount of p-doped and n-doped strips will send a signal. Since every hit could have been a potential particle, the DAQ must transmit all signals. This leads to higher background for the SVD in regions close to the interaction point (IP). To overcome these huge backgrounds the inner radius only reaches down to 38 mm from the beam axis and then two layers of pixel-based readout are placed. In figure 3.5 a 3D model is shown.

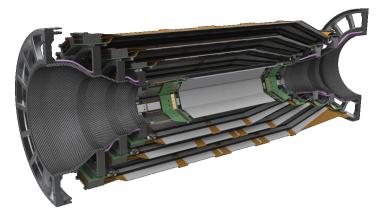

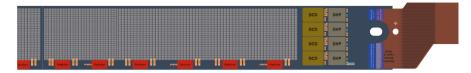

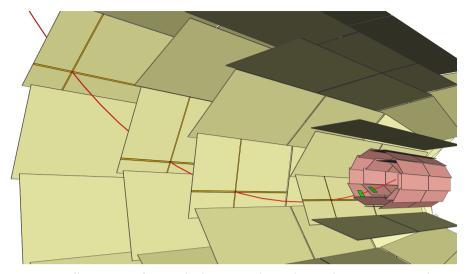

## **3.3 The Pixel Detector (PXD)**

The inner most detector of the Belle II experiment is the *pixel detector*. The Belle II Technical Design report [21] includes an comprehensive report about it. It consists of two layers of sensors, arranged like the SVD, around the interaction point at 14 mm and 22 mm. In total 40 PXD modules are present, illustrated in figure 3.6. Since this thesis deals directly with the data processing of this subdetector, it will be described in more detail. The physical requirements will be discussed, as well as the exact detection mechanism and the readout and processing of the data. Chapter 4 describes the further processing of the detector data. Figure 3.7 shows the PXD system including supporting frame and cables.

Figure 3.6: Rendering of a PXD module (forward direction, outer layer), by the DEPFET collaboration. On the right side attached Kapton cable connects to the outside. The ASICs are placed next to the active sensor matrix.

Figure 3.7: Photograph of the mounted PXD.

## **Background Exposition**

Before making assumptions about the performance and feasibility of the detector, it is necessary to understand the different background processes to which this detector is exposed. These processes fall in two categories [32]:

## Beam-induced processes

arise from the two beams independently rather than from collisions between them. It is generally proportional to the beam current, which only increases by a factor of approximately 2.2 compared to Belle. During its turns in the beam line, a Gaussian shaped beam-bunch loses charge. In order to determine a beam lifetime, it is necessary to consider the typical timescales for each process that contributes to charge losses. Such processes cause particles to cross bunch boundaries and collide with beam pipes, which in turn produce particle showers that, when within the range of a detector, produce unwanted signals overlaying the hits from physics events as background. One of the most relevant processes responsible for beam background is the *Touschek effect*, which involves the intra-bunch scattering of two electrons or positrons. This effect increases with lower beam size, which due to the nano-beam scheme is very small.

A further process reducing beam lifetime and contributes to background is *beam-gas scattering*, which occurs when beam particles escape the bunch and interact with residual gas molecules in the beam pipe.

Lastly, *synchrotron radiation* is the result of charged particles being accelerated, causing a photon to be emitted. The electron and positron beams produced at SuperKEKB are deflected by quadrupole magnets to keep them in the circular beam pipe. Magnets before the interaction point focus the beams, which contribute to additional background hits in the detector.

#### Luminosity-dependent processes

are induced by QED interactions of electrons and positrons, directly associated with beam collisions. The predominant source is the dominant *two-photon process*.

$$e^+e^- \rightarrow e^+e^-\gamma\gamma \rightarrow e^+e^-e^+e^-$$

Since they are directly dependent on instantaneous luminosity, their rate is expected to be 30 times higher than at Belle. During the photon-photon interaction, low energetic electrons and positrons curl in the magnetic field, leaving signals only in the PXD.

*Bhabha scattering* is another source of background from QED processes. Colliding electrons and positrons do not annihilate but scatter. Afterwards, these scattered particles leave the interaction region under very small angles and are converted into secondary particles in the beam pipe.

Based on a background simulation [32], the occupancy is calculated. It describes the number of hits relative to the total number of PXD pixels in a single event. All background sources add up to 1.74% occupancy. Less than 0.1% of the pixels are triggered by actual signal hits, which are useful for later analysis. In light of the hardware limit of 3%, the PXD should function effectively under the expected conditions. Assuming that the design trigger rate is 30 kHz, the total PXD data rate is around 20 GB/s. This requires a dedicated data acquisition system with fast readout and reduction capabilities to handle background dominated data.

The actual background situation of the full Belle II detector in 2021 is summarized in the Snowmass 2021 paper [33].

## **Detection Mechanism**

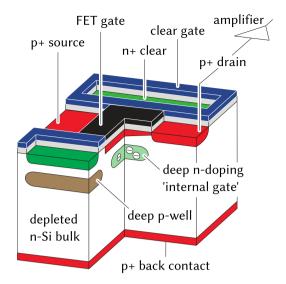

For the detection, a depleted field-effect transistor (DEPFET) [34] is used. This detector technology is utilized in Belle II as part of a particle physics experiment for

Figure 3.8: Illustration of a single DEPFET pixel.

the first time. In order to achieve a good vertex resolution, multiple scattering of particles within the detection layer must be kept as small as possible. Consequently, the thickness of the sensitive area was of high importance. The DEPFET technology allows a thickness of only  $75 \,\mu$ m.

The figure 3.8 illustrates the main features of a DEPFET pixel that is composed of silicon soils (bulk) grounded on positive contacts and topped with p-channel MOSFETs<sup>1</sup>. The positive grounding plate causes the bulk region of the DEPFET to become fully depleted. At the same time the p-doped ground plate acquires a negative potential. An electron-hole pair is created in the silicon soil by ionization of a traversing electron. Positively charged holes drift to the ground plate while electrons accumulate in a potential minimum below the gate. When the gate is active, it is possible to measure the drain current, which is directly proportionate to the electron count. In order to perform the next measurement, the electrons within the internal gate need to be cleared once the drain current has been measured and the amplified signal has been sent down the data acquisition chain. When a positive potential is applied to the clear gate, electrons will drift to that location and allow a new readout cycle to take place.

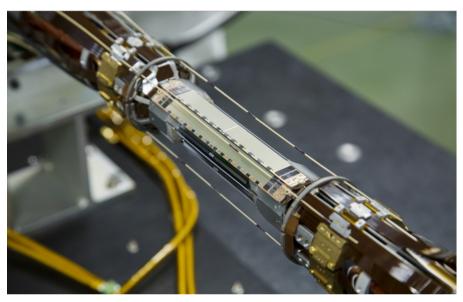

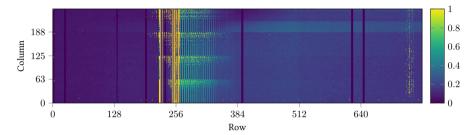

DEPFET pixels are arranged in an array of  $768 \times 250$  for a single module. Each pixel measures  $55 \,\mu\text{m}$  times  $60 \,\mu\text{m}$  in the inner layer and  $70 \,\mu\text{m}$  times  $80 \,\mu\text{m}$  in the outer layer. With the supporting frame the thickness is increased to  $420 \,\mu\text{m}$ . All modules have a sensitive area with a width of  $12.5 \,\text{mm}$ , extended to  $15.4 \,\text{mm}$  by the supporting structure. The length varies between the inner and outer layers. While the sensitive area in the inner layer measures  $44.8 \,\text{mm}$ , the length is slightly higher

<sup>&</sup>lt;sup>1</sup>Metal Oxide Semiconductor Field Effect Transistor

in the outer layer at 61.44 mm. The frame extends each module to 68 mm for the inner layer and 85 mm for the outer layer. The surrounding rim increases mechanical stability and provides space for application-specific integrated circuits (ASICs), which are essential for control and read-out as well as voltage supply. A flexible printed circuit (Kapton) establishes the connection to external control systems and power supplies.

## **Read-Out**

A DEPFET module has 250 long columns and 768 short rows of DEPFET pixels arranged in a matrix. Electrically these pixels are rearranged by combining four rows into a row group, yielding an array of 1000 logical columns, called *drain lines* and 192 logical rows, called *gates*. The modified logical structure results in an increased readout speed. The voltage is applied to the DEPFET in such a way that the accumulated charge can flow to the ADC via drain lines. All logical columns are read out simultaneously, while only one logical row is supplied with the necessary voltage. The logical rows are processed one after the other to ensure readout and complete discharge. This way 192 pixels are connected to the same ADC channel.

The readout of a module requires three different ASICs [35], which are placed directly next to the matrix.

#### Switchers

The six switches apply the gate and clear voltage. All pixels within a logical row are operated at the same voltage. There are three operating modes. While both voltages are held back, charge can be deposited in the sensor. The module is in this state until the readout of this row is started. Then the gate voltage is applied, so that readout is possible via an ADC. The clear voltage is added with a delay to clear the collected charge. The readout and clear of a row takes about 100 ns before the switcher continues with the next row. With almost 200 rows, the complete readout of a module takes  $20 \,\mu\text{s}^2$ .

## DCDs

4 DCDs (drain current digitizers) [36] convert analog to digital signals. Each DCD has 256 channels with 8 bit resolution. Additional features like individual offset correction and adjustable gain and bandwidth allow individual adaptation to each sensor. Dark currents can be individually subtracted, increasing the dynamic range of the ADC. The load of 1000 logical columns is measured via the drain line on all DCDs. After processing, the data is sent to the respective control center, the DHP, via eight 8-bit links.

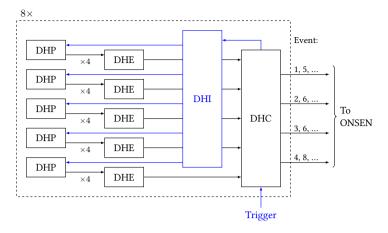

### DHPs

4 DHPs (data handling processors) [37] store incoming data in a ring buffer. The buffer size is selected so that the data of an entire module can be buffered twice. This ensures that all data from the last complete readout is available even after the trigger signal arrives. DHPs can configure DCDs via JTAG connections. At the same time, one of the DHPs controls the voltage sequencing of all switchers. With the trigger signal, further processing is started and data is forwarded via high-speed optical links. During processing, digital pedestal offsets are subtracted from each pixel value. This offset can be set individually for each pixel and is usually determined using raw data.

$<sup>^2</sup> For$  comparison, each bunch in the accelerator passes the interaction point twice during 20  $\mu s.$  Therefore the charge and number of signals are accumulated for multiple events.

## **Chapter 4**

# **Data Acquisition**

Due to the complexity of the Belle II detector, it is not possible to analyze the analog signals on the fly. Instead, the information must be stored for later offline analysis. Therefore, the signals from each detector component must be read out, digitized and stored. The conversion of analog signals to hard disk storage is the purpose of the data acquisition (DAQ) of the Belle II detector. Although the DAQ is available from the previous Belle detector, the level of detail and trigger rate is increased and requires an upgrade of the entire DAQ system. The 40-fold increase in data rate of the predecessor is not being dealt with by the existing implementation and an upgrade in hardware and software is foreseen. Six gigabytes of raw data per second will be produced by the outer detectors, while the high resolution of the PXD will result in more than 15 gigabytes of unfiltered data per second.

The data handling of the outer detectors is unified at each step of the data acquisition chain in order to minimize the maintenance cost to operate the system for more than a decade. The PXD has a separate data acquisition and all raw data is truncated before being written to disk. This behavior is explained in this chapter.

## 4.1 Belle II DAQ Overview

## 4.1.1 Trigger System

The data from the Belle II experiment is separated into individual events. Each event is issued by a trigger system linked to the Belle II physics program. Each field of interest can be described by the subdetectors using a variety of characteristics. Configurable logic based on FPGAs allows a fast response after combining raw signals and generating a draft version of an analysis. If the signature of this rough analysis matches any of the predefined characteristics of interest, a single trigger signal is issued.

Many of the pre-defined signatures contain signals from at least two charged particles with their tracks coming from the interaction point. The charge and track direction can be extracted from the CDC and ECL, which serve as the main input for this rough analysis. The calculation of the energy deposition of a cluster in the ECL with its track shape allows to distinguish between different types of electromagnetic processes. Additional timing information from the ARICH and the TOP or the presence of muons from the KLM can provide further information to trigger events. With redundant tracking and calorimeter trigger information, Belle II provides greater than 99 % efficiency for *B* meson events.

All channels send their data to the *global decision logic* (GDL) [38, p. 1], summarizing the available signals and creating a final trigger signal. The GDL configuration allows to mask or pre-emphasis certain channels, if necessary. The final trigger signal is forwarded to the *frontend timing switches* (FTSW) [39], an FPGA based distribution system, which ensures simultaneous readout of the frontend digitization boards of the most recent data. Multiple FTSWs are arranged in a tree-like structure. The main FTSW generates a *level-1* trigger signal that includes precise timing information and an event number that automatically increments with each received signal.

Based on a study of Belle, the level-1 trigger rate is expected to be nearly proportional to the luminosity and is approximately 20 kHz at the design luminosity [40]. With contingency, the entire data acquisition system is designed for a trigger rate of 30 kHz.

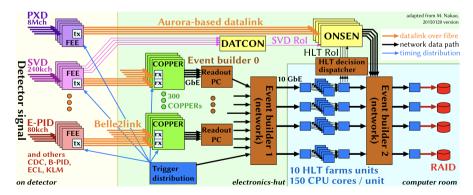

## 4.1.2 Data Flow

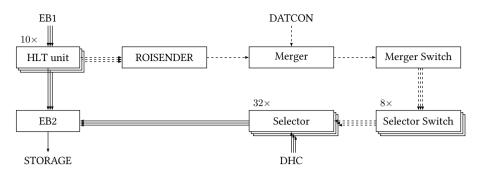

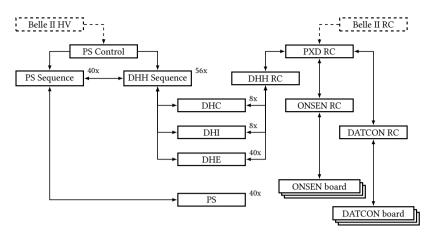

When the trigger signal arrives at each subdetector, the readout is started by the fronted digitization boards. The data flow is illustrated in figure 4.1. The detailed stages are described in the following sections. The PXD system has a completely different time and readout structure and its data stream is separated until the last stage.

Figure 4.1: Overview of the Belle II data acquisition system.

#### FEE

All subdetectors provide dedicated hardware directly connected to their sensors to handle the low level configuration and start the readout process after receiving a trigger signal. This *front-end electronics* (FEE) is based on FPGAs or ASICs to process the trigger signal as fast as possible and to stream the necessary information as raw data to the next level. The analog pulse information is already digitized at this first stage. Different data schemes are configurable to take different data for physics or calibration data acquisition.

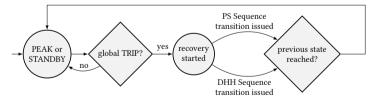

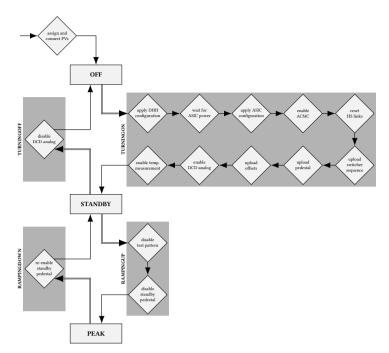

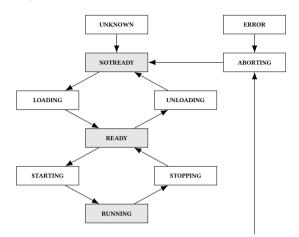

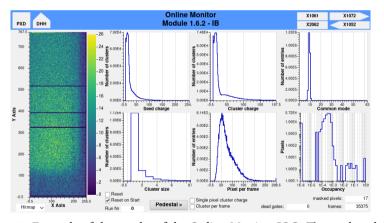

#### **COPPER** (Digitizer)